工具/软件:

我已将 DAC80508 EVB 连接到 STM32U5 Nucleo 测试板。 DAC 片选 (CS) 应由微控制器通过 DMA 和计时器 (PWM) 驱动。

我将发送 4 个样本、每个样本都是 32 位字。 DAC 默认配置为异步模式。

当通过代码基驱动的 CS 从代码更新 DAC 时、DAC 的输出会在 CS 变为高电平后立即更新。

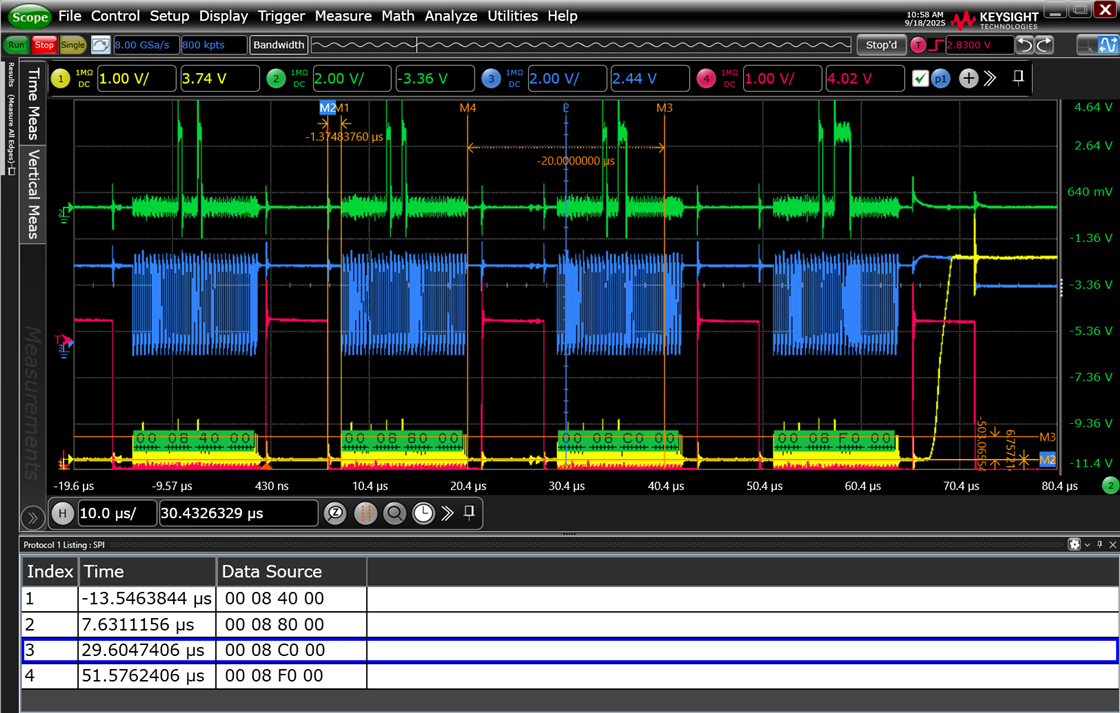

当通过 PWM 计时器驱动 CS 并使用 DMA 将样本移出时、示波器上的一切看起来都相同、所有时序都远远超出数据 pec 限制。 但是、DAC 不会更新前 3 个样本的输出、只有在第 4 个样本之后才会更新输出。 它始终是最后一个、即使发送 100 个样本也是如此。

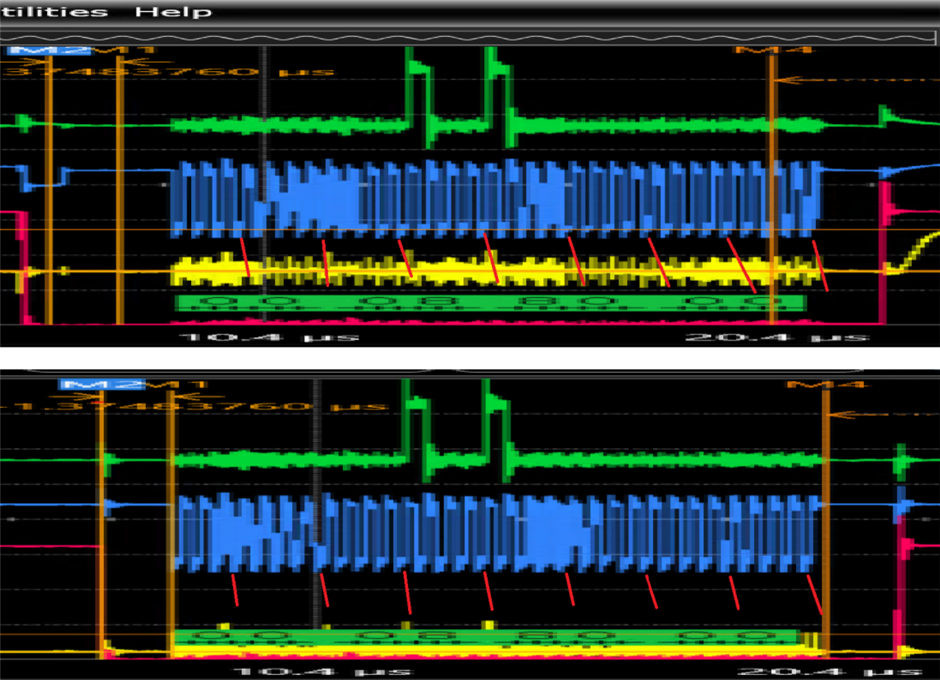

Pic1:代码驱动的 CS、工作正常、CS=红色、CLK=蓝色、数据=绿色、 DACout=黄色

Pic2:计时器驱动 CS、DMA 驱动采样、DAC 输出不工作、 、CS =红色、CLK =蓝色、数据=绿色、 DACout=黄色

我怀疑、只要 ST 主动保存 CLK 引脚、DAC 就不会更新输出。 如第二张图所示、蓝色 CLK 由微控制器保存、只有在通过 DMA 发出最后一个样本后、似乎才会释放 CLK(向上小勾号)、正是在这之后、DAC 才会更新其输出。

当 CS 由代码驱动且每个样本单独发送时、CLK 始终显示向上小勾号(图 1)、这似乎是 DAC 更新其输出的触发器。

我正在寻找该行为的说明、因为 DAC 数据表未提供这方面的详细信息。