Other Parts Discussed in Thread: TI-JESD204-IP, ADC12QJ1600

主题中讨论的其他器件:TI-JESD204-IP、 ADC12QJ1600

工具/软件:

您好:

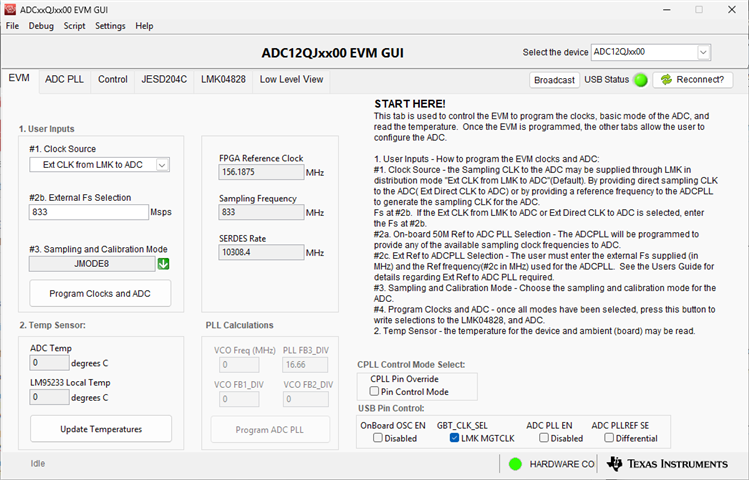

我正在使用 ADC12QJ1600 EVM 和 TI-JESD204-IP、对如何配置 ADC12QJ1600 EVM GUI 存有疑问。 我已将 JESD IP 设置为 64b/66b、使用 4 个通道接收、并相信通过连接到 LMK CLK 的外部时钟、我可以将模式传递到应在 ILA 上查看的 FPGA。

我认为我的约束是正确的(ADC 的 FPGA_GBTC0_FMC 映射到 IP 中的 REFCLK、FPGA_SYSREF_FMC 映射到 sysref、FPGA_CLK_FMC 映射到 sys_clk,以及数据通道)。

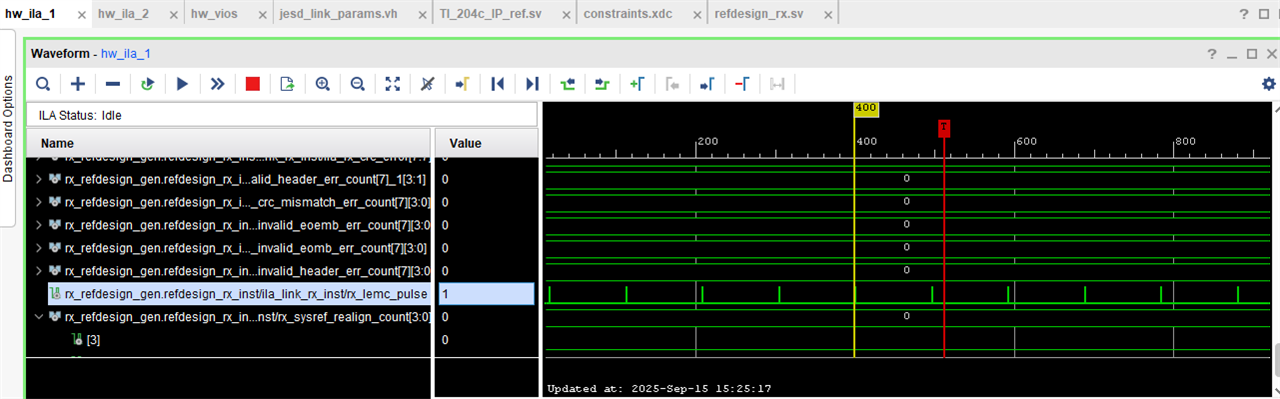

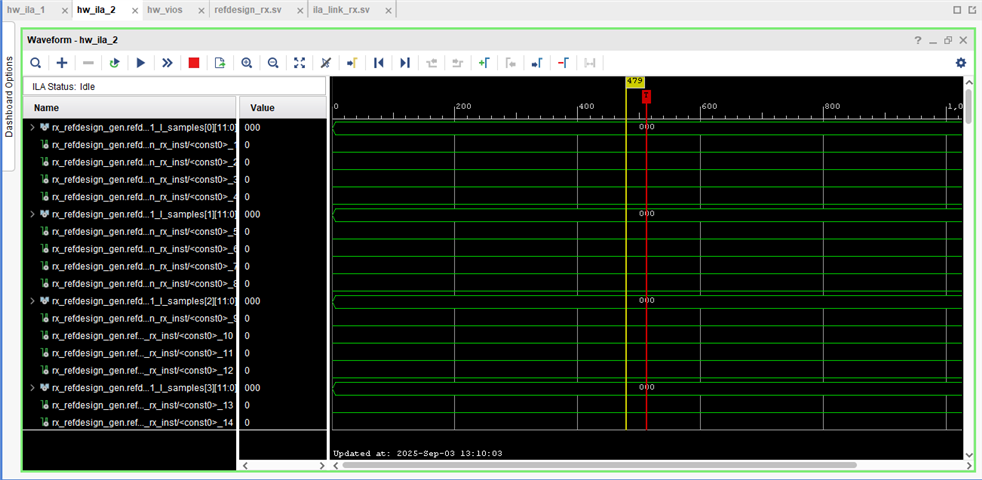

我首先使用 JMODE8 和 833MHz 外部时钟、因为这会导致通道速率和 FPGA 时钟类似于 JESD-IP 中的默认时钟、因为我只想看到任何信号通过、并更改了 JTEST 寄存器以尝试斜坡和传输测试模式、但在 FPGA ILA 中看不到任何结果。

我希望有人帮我完成所需的设置、我需要更改这些设置、使 ADC 与 IP 兼容、在 ILA 中显示信号、这样我就可以确认 ADC 和 JESD IP 设置正确。

谢谢你。