请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TI-JESD204-IP主题:ADC09DJ1300 中讨论的其他器件

工具/软件:

您好、专家、

我无法解决 Vivado 时序分析中的脉冲宽度错误。

(错误屏幕)

利用此配置是否可以保证 ADC09DJ1300 和 TI-JESD204C-IP 的运行?

是否可以将它们用于此设置?

如果有我可能忽略的任何设置、请告知。

(设置)

器件:

ADC09DJ1300

TI-JESD204C-IP Release-v1.10-latest

Xilinx Zynq-7000 xa7z030fbv484-1Q

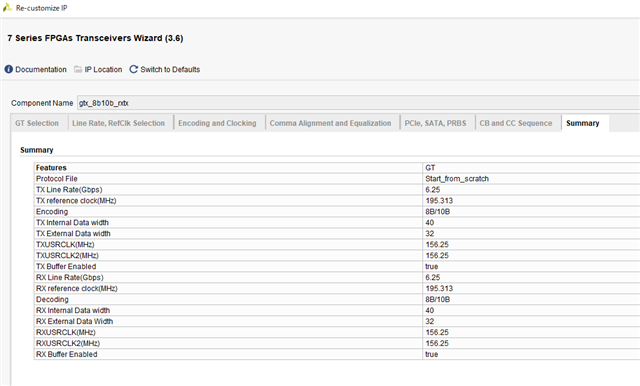

设计参数:

双通道模式

采样 1.25GSPS

JMODE 9 (8 位、4 通道、8B/10B)

JESD204C 子类 0

LineRate 6.25Gbps

主机 PC:

Vivado 2022.1

Win11.

(Vivado Tranceiver Wiz)

谢谢你。