Other Parts Discussed in Thread: ADC3563

工具/软件:

您好、

我正在使用 ADC3563、并尝试使用内置斜坡测试模式来验证所有 LVDS 通道。 我的设置配置为 32 倍双频带复数抽取、因此我期望在 DA 和 DB 通道上都看到相同的斜坡模式。 我在 AI 的帮助下准备了这个问题、但它确实显示了我的问题。 AI 只是找到更好的解释;-)。 希望您不介意。

观察结果:

-

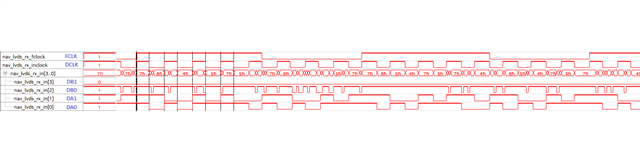

DA 通道 (DA0/DA1) 工作正常。 我看到与 FCLK 和 DCLK 匹配的同步数据模式。 我尚未对 FPGA 内的数据进行解串。

-

DB 通道 (DB0/DB1) 不工作。 我看到的是看起来像噪声的高频异步信号。

系统配置:

-

器件:ADC3563

-

采样时钟 (FS):15.3104MHz

-

串行器时钟 (DCLKIN):3.8276MHz

-

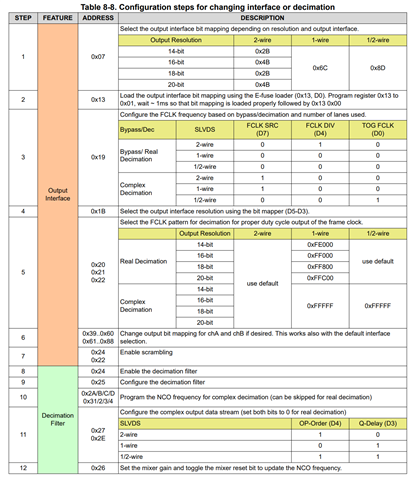

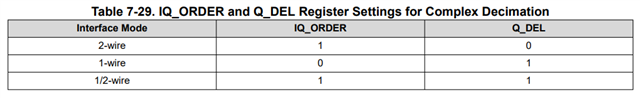

模式:2 线、16 位、32 倍复数抽取率、双频带

-

硬件:外部 100 Ω 差分端接经验证存在于 FPGA 的所有 LVDS 输入对 (DA 和 DB) 上。

寄存器初始化序列

以下是硬件复位后我要发送到器件的 SPI 写入的确切顺序:

我的问题:

鉴于 DA 通道在此配置下工作似乎合理、是否缺少完全启用 DDC B 数据路径和 DB0/DB1 LVDS 驱动器所需的任何寄存器设置? 根据数据表、配置似乎是正确的、但 DB 通道上的行为指示存在问题。

感谢您的支持。