工具/软件:

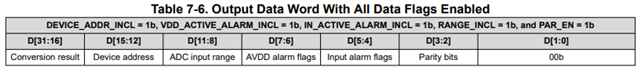

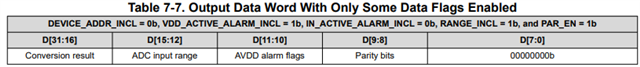

您好 — 我有一个由 FPGA 控制的 ADS8681 定制电路板。 我的 SPI 接口正常工作、我可以将数据输出寄存器设置为输出 01 或 0011、返回的 16 位数据是 x5555 或 x3333。 如果将 ADC 的输入端接地、则会得到 ADC 数据的 X8000 (+/- 3 LSB)。 我配置 rst_pwrctl_reg 来启用输入警报和 AVDD 警报、而这个警报是在数据输出寄存器中设置的。我将位 13:10 设置为“1111",“,这样、这样我就可以为两个警报同时获取高电平和低电平标志。 我的问题是、如果触发警报、将在哪里设置高和低警报位? 在第 42 页的表 7-6 和 7-7 上、警报标志位于不同的位位置。 我不需要器件地址、输入范围或奇偶校验位、只需要 ADC 数据和 4 位警报标志。 这些标志将用于关闭系统的另一部分。 谢谢你。