Thread 中讨论的其他器件:ADS54J60EVM

工具/软件:

您好、专家

我很难在 FPGA zcu102 板中实现 JESD204 IP 接收器。

首先、我已经使用 TSW14J50 检查了 ADC ADS54J60EVM。 (SerDes = 4.9152Gb/s、器件 frequeny = 983.04MHz、LMFS=8224、函数发生器频率 100MHz 10dBm 功率(对于 CHA)和 100MHz 4dBm(对于 CHB)。它成功运行、 如下方所示

接下来、我仿真了 TI JESD204 IP 设置 IP_TYPE “RxTx"。“。 在 TI_204C_ip_ref 的仿真中、我的 gth_8b10b_xcvr 显示在下面的两个图中

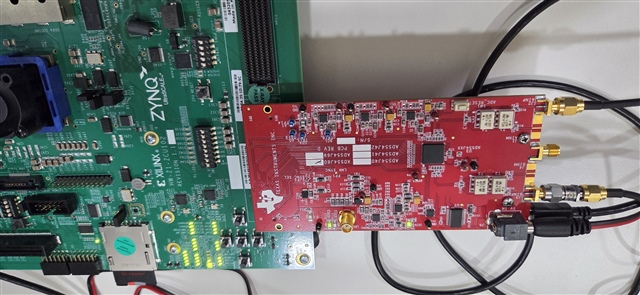

REFCLK 245.76MHz 用于 使用 BUFG_GT 生成额外的 245.76MHz mgt_gpio_out 时钟。 该 mgt_gpio_out 用于 sys_pll 的 clk_in 输入、可生成两个频率相同的 61.44MHz sys_clock 和 mgt_freerun_clock。 通过在 TI_204C_IP_ref 中传递 vIO_inst 仿真成功运行。 最后、我为设置 IP_TYPE “RX"的“的接收器制作了位文件。 设置显示在照片中、如下所示。

测量结果显示在下面的中、很遗憾、rx_lane_data_valid 保持为 0、因此所有 rx_data 0。

我不知道为什么 ADC 接收器无法工作。 起初我使用了 si570 等 FPGA 时钟、但 sys_clock 和 mgt_freerun 时钟频率并不准确。 因此、我使用 mgt_gpio_out 进行了更改、其频率 完全等于 REFCLK。 我想 让 ADC 接收器正常工作。 提前感谢您。

此致

K.W. Yeom