工具/软件:

您好:

我想我遇到的相关问题是相同的。

我认为一切都设置正确、以便在连续模式下重试数据。 fSCLK 设置为 2MHz、SPI 模式 3。

但即使我在输入通道上放置了一些电阻器(具有不同值)、通道 1 至 7 的数据也绝不会相同。

我正在使用 ADC128102EVM 连接到 Microchip SAMRH71 微控制器。

您是否有任何建议可以了解是否存在某些 SPI 配置错误?

谢谢。此致、

Enrico

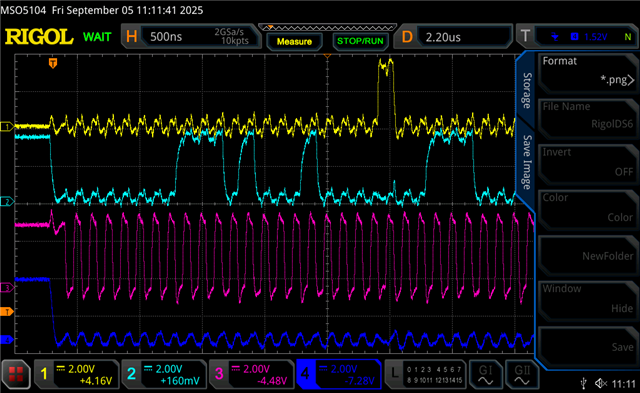

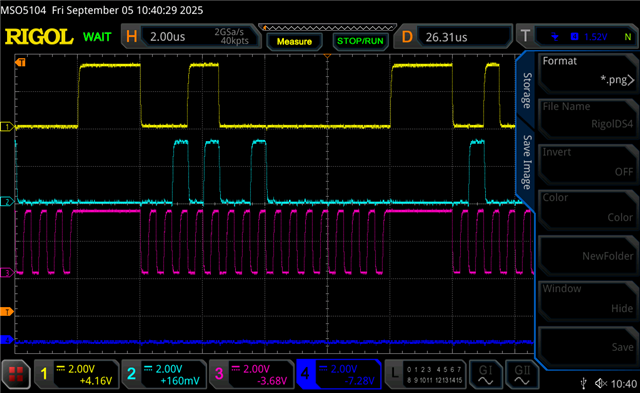

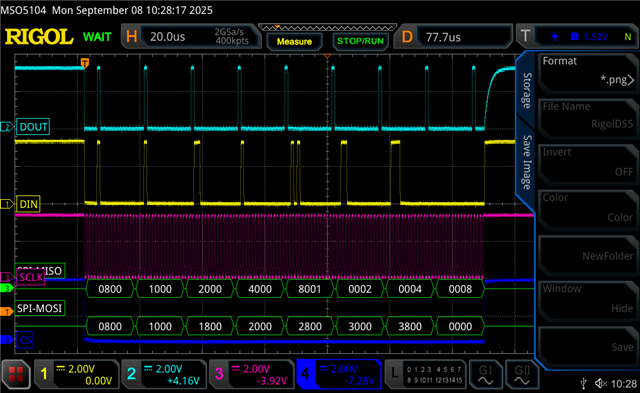

黄色:MISO

浅蓝色:mosi

紫色:CLK

蓝色:CS

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好:

我想我遇到的相关问题是相同的。

我认为一切都设置正确、以便在连续模式下重试数据。 fSCLK 设置为 2MHz、SPI 模式 3。

但即使我在输入通道上放置了一些电阻器(具有不同值)、通道 1 至 7 的数据也绝不会相同。

我正在使用 ADC128102EVM 连接到 Microchip SAMRH71 微控制器。

您是否有任何建议可以了解是否存在某些 SPI 配置错误?

谢谢。此致、

Enrico

黄色:MISO

浅蓝色:mosi

紫色:CLK

蓝色:CS

尊敬的 Enrico:

因为我不在办公室、所以对迟来的答复表示歉意。

为了进行验证、您是否看到了 套件中包含的将 ADC128102EVM 连接到 PHI 控制器时的预期结果?

https://www.ti.com/tool/ADC128S102EVM

您能否更深入地解释以下步骤? 我认为最简单的方法是将电源连接到输入端来验证输出代码。

[引述 userid=“669243" url="“ url="~“~/support/data-converters-group/data-converters/f/data-converters-forum/1560601/adc128s102-adc128s102但即使我在输入通道上放置了一些电阻器(具有不同值)、通道 1 至 7 的数据也绝不会相同。

[/报价]您是否还能够在不 叠加逻辑分析仪的情况下发送示波器图? 以这种方式查看图会有点困难。 DOUT 应始终以 4 个零开始、因此 MISO 上的第一个数字应始终为零。 在捕获中、情况并非总是如此、因此很可能存在一些错误配置。

此致、

Joel

尊敬的 Joel:

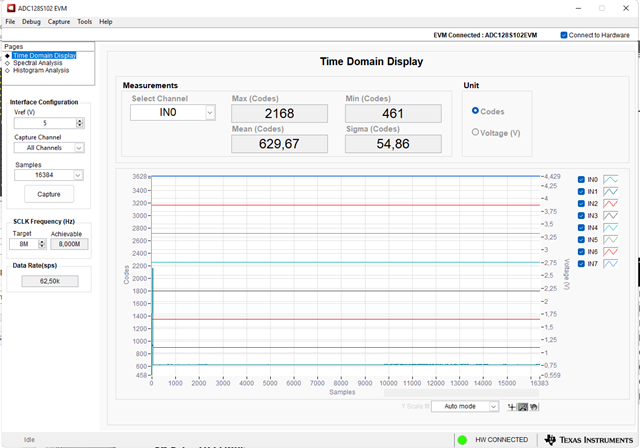

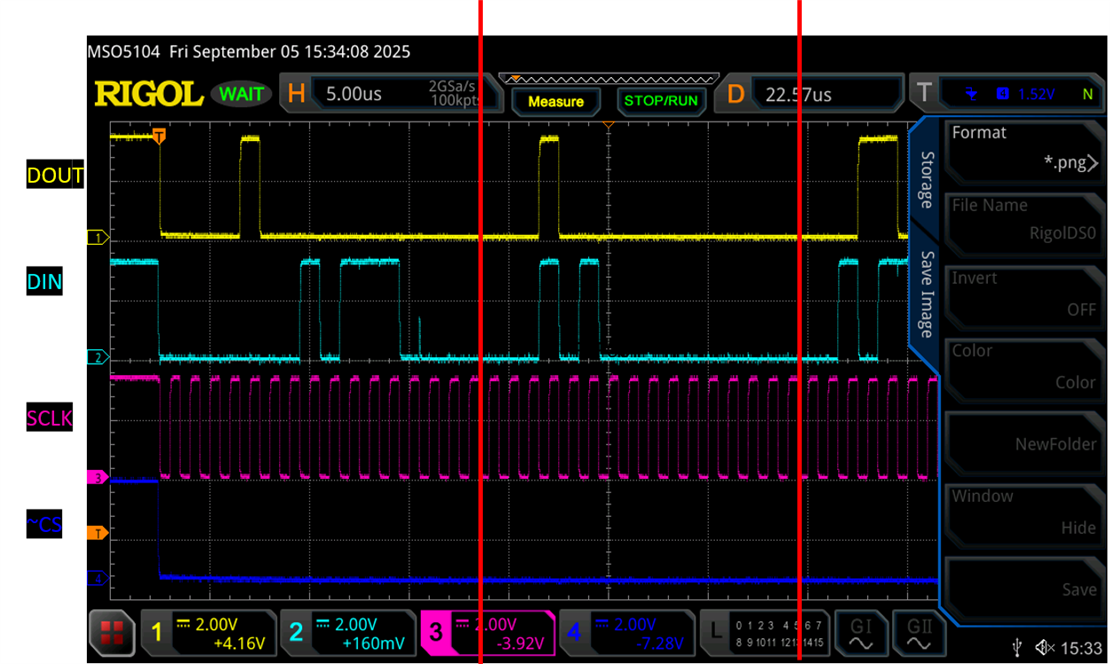

我尝试了 TI GUI、可以看到一切都按预期运行。 (请参阅下面的信号顺序为 MOSI、MISO、CLK、CS)

然后我尝试设置、请参见下图。

我想做的过程是通过单个 SPI 通信获取所有通道(连续模式)。 SPI 输出缓冲器由通道 1-channel7 地址+通道 0 地址充电、以获取通道 7 测量值。 该设置为为 EVM 提供 3、3V 的电压。

我遇到的是、信道从不会以相同的值响应、并且不在范围内。 也不会看到响应中的前导 0。

同样、通道 0 响应的值似乎与 GUI 接收到的值相同。 (0x170/0x180 VS 0x1D1/0x1C7)

我能看到的主要区别是时钟有一段时间被卡住、不知道此时为什么会这样。 我管理与中断的 SPI 通信、以更新输出缓冲器。 你认为这是个问题吗?

我还将采用较低频率 (2MHz)

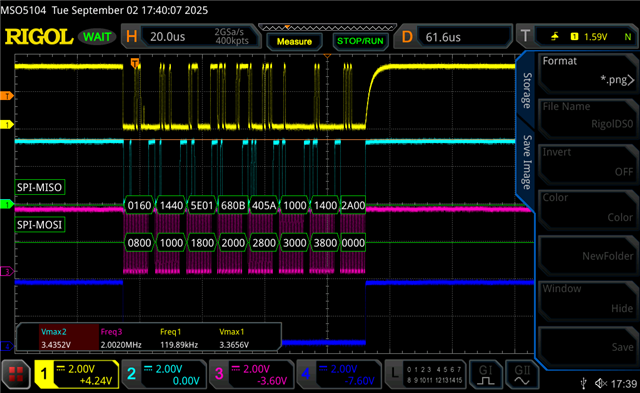

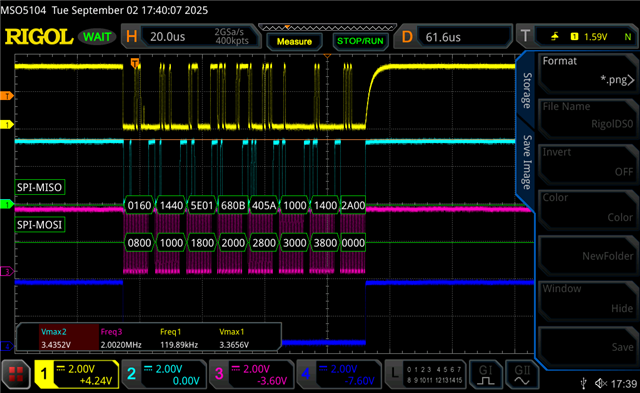

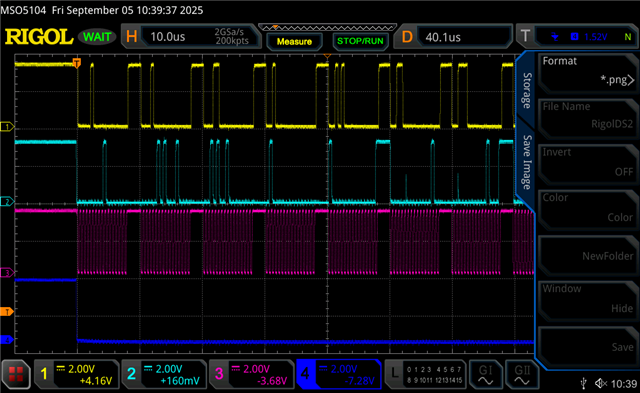

所有通道:

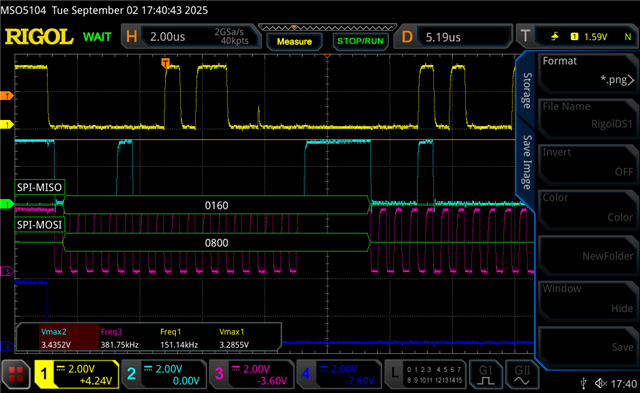

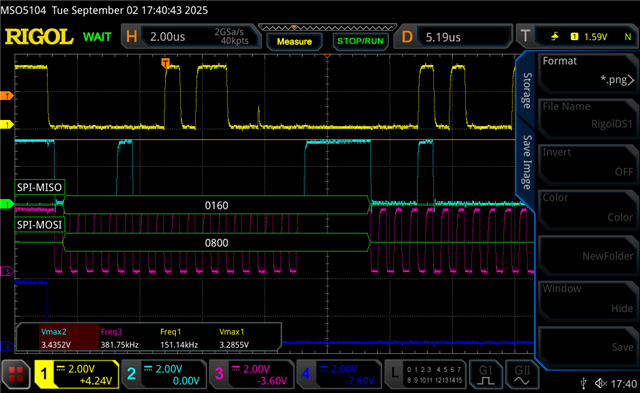

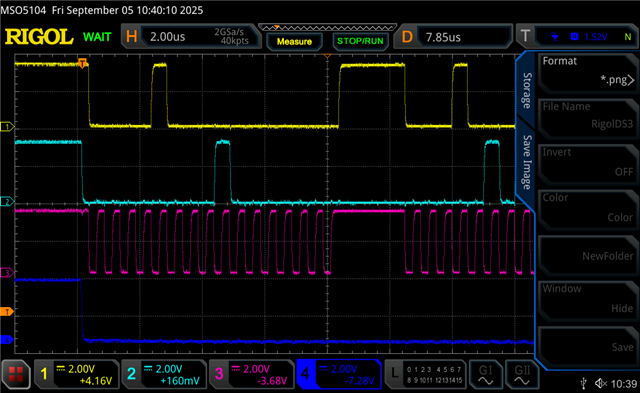

通道 0 响应

通道 1 响应

谢谢。此致

尊敬的 Enrico:

感谢您分享这些捕获内容。 我继续,并标记了图像显示的问题只是为了使它更容易看到。 红线取消 SPI 帧结束的标记。 数据的提供时间似乎比我们在数据表说明中预期的要早一点、

DIN 上发送的数据是什么? 它似乎与应在第 3 个、第 4 个和第 5 个时钟上发出 ADD[2:0]位的位置不对齐。

您可能能够尝试的一件事是将输入连接到 AVDD、以便输出 0xFFF。 那么、可能会更清楚地看到这四个零点。

DIN 上也有有趣的行为、在第 14 个下降沿略有过渡。 是否了解控制器此时可能尝试执行的操作?

此致、

Joel

尊敬的 Joel:

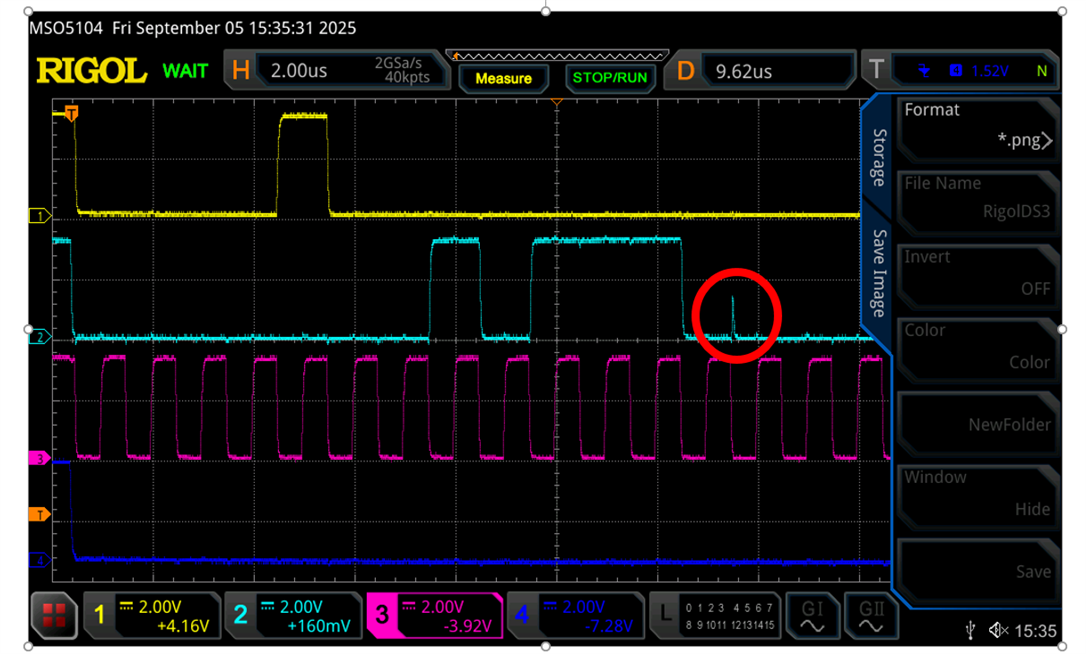

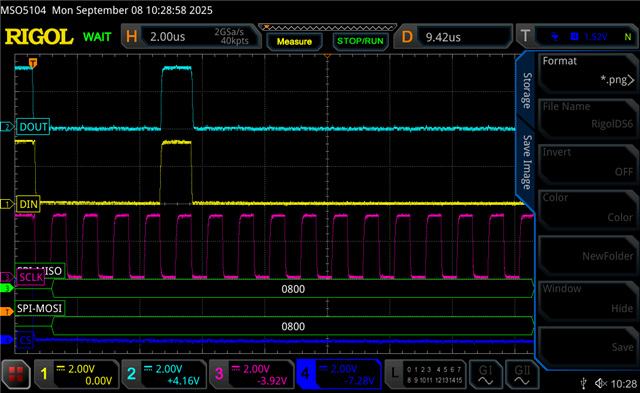

我想我已经与信号描述混淆了。 现在、我根据 ADC128S102 引脚排列放置了标签。

在我的 understanding 地址是对齐 他的第三,第四,和第五时钟上升的前面。 我的回答正确吗?

第一个图像是通道 1 的第一个地址请求。

第二个图像报告了我当前发送的地址序列以及下面的转换结果。

在下面的两个图中、我还将通道 0 和通道 1 的输入连接到 AVDD、但您可以看到、我没有接收 0xFFF...

我无法理解错误配置在哪里... μ s

我添加了另一个奇怪的行为:如果我将通道 0 和通道 1 连接到 VDD 也其他输入改变响应... 不确定这是否可以添加信息…

感谢您的观看、

此致

尊敬的 Joel:

我在下面回答你的一些问题

您能尝试在上电后立即从通道 0 进行转换吗? 可以同时断开 DIN。 [/报价]您能更好地描述一下吗?

谢谢。此致

尊敬的 Enrico:

R39 是否也断开连接? 由外部供电时、PHI 板是否仍连接到 ADC128S102EVM? EVM 电路板上的何处连接了电源、AVDD 和 DVDD 如何短接?

我要说的是、由于 ADC 通道是通过 DIN 引脚选择的、如果它与控制器断开连接、它将读取全 0、并始终选择通道 0。 这样、可以保证 DOUT 上的输出实际上对应于通道 0。 DIN 也可以接地以确保安全。

仍然将 AIN0 短接至~您仅提供器件的 CS 和 SCLK、是否在 DOUT 上获得任何高电平位?

我也有另一个怀疑。 EVM 电路板的输入由放大器驱动。 这些放大器由 LDO 生成的 5V3 电源轨供电。 该 LDO 通过 PHI 控制器直接由 USB 电源供电。 可能是输入连接到放大器输入、而放大器未通电、因此输出不正确?

此致、

Joel

您好 Joel、

很抱歉、我没有很好地解释设置。

1.使用 PHI+EVB 设置

在这种情况下、我将 PHI 连接到 J25 连接器、并使用 USB 为 PHI 供电。 在此设置中、外部电源已断开、但 R42 不存在(R39 存在)、并且 VA 和 VD 之间存在短路。 【短接带外部有线连接,实验室鳄鱼夹】

移除 J26 上的 SPI(来自 Microchip 电路板)连接、并将这些引脚连接到示波器。

2.与 Microchip Dev 电路板的设置

在这种情况下、从 J25 连接器上移除了 PHI。 R42 不存在、R39 存在。 VA/VAA 上的短路相同 VD。 外部电源 (3、3V9 直接连接到 VA。

J26 上的 SPI 连接与 Microchip 开发板和示波器连接到导线上。

输入通道的连接在两种配置之间不会改变。 跳线 J1、J7、J13……(依此类推)连接到旁路运算放大器、或者这是我们的用途(跳线连接在写入 “旁路“的一侧)

我要说的是、由于 ADC 通道是通过 DIN 引脚选择的、如果它与控制器断开连接、它将读数为全 0 并始终选择通道 0。 这样、可以保证 DOUT 上的输出实际上对应于通道 0。 DIN 也可以接地为[/报价]Unstand。 今天我无法重做测试,但我很确定,在前一个测试中,我尝试发送通道 0 请求所有 8 通道。 我是在软件上编写的、因为它更简单、我会检查示波器上的输出。 无效的 ADC 转换导致相同的结果。

μ s

设置 2 是因为 Microchip DEV 电路板配置为管理 3.3V 稳压器(这将是我们的 PCB 准备就绪时的实际工程状态)。 所以我们害怕混合不同的基准电压。

您能提出连接评估板的理想方法吗?

此致、

尊敬的 Enrico:

感谢您分享完整的设置。 从描述来看、一切似乎都是正确的。 也许分享图片也有助于发现是否有任何问题? 还要探测引脚上的实际电压。

否则、我要指出的是、确保遵守时序特性、尽管目前我在查找任何可能出错的问题时遇到了问题。

我将通过使用 EVM 进行测试并在 MCU 和 PHI 控制器之间来回切换、再次检查器件是否未损坏。

除此之外、我想不出还有什么可以检查的、因为这是一个相对简单的器件。 我已经反复检查了数字,从你的描述的电源似乎是好的,输入似乎也很好。 我认为我们没有讨论过接地、但可能这也很好。

我将阅读整个线程以检查我是否错过了任何明显的东西,但如果你能够验证以上所有内容,这将是非常有帮助的。

此致、

Joel

您好 Joel、

也许我有一些新闻,即使通信仍然不好. 也许您可以帮助我找到根本原因。

因此、我尝试使用 PHI 板进行设置(下图,我知道设置不清晰...) 一切正常。 但这种设置触发了我! 我之前提到过、R42 断开连接、VA 与 VD 没有短接。 然而,与 GUI 的转换是相当好的(也有示波器; 0xFF9 0XFFA 与 Ain0 短接至 VD 和 0x000 短接至 GND)。

让我怀疑的是 VA 上未连接到 VD 的电压、大约为 4V。

我尝试用演示板复制设置、设置完全相同、但 VA 短接到 VD、SPI 通信连接到演示板。

SPI 通信无法正常工作 、我看到连接到 GND 的通道 报告 0x000。 μ s

然后、我尝试移除 VA、连接到 GND 的通道仍在 SPI 上报告 0x000

因此、我们尝试(我公司聘请了硬件人员)来简化设置、移除了输入通道的所有连接、并将所有通道短接至 GND、如果需要、所有通道都会在 SPI 上报告 0x000。

这似乎是一个解决方案、但它不是

我尝试仅将 1 个通道连接到 VD、然后收到虚假数据。 我们还测量 VA 上的电压、约为 2-4 伏。

简短介绍 VA/VA/VESEEms VD、让事情变得更糟。

我们执行另一项测试。 我们从演示板断开所有连接、只保留与 GND 和 VD 的连接、移除了所有跳线。

然后我们测量 Va、得到图中所示的 2.484V。 这对你有意义吗?

所以我认为设置有问题,而不是 SPI 通信本身..

您能帮助我了解哪种配置很适合在没有 PHI 板的情况下为演示板供电?

谢谢。此致、

注意:在使用 PHI 板的第一步中、我尝试将 VA 连接到外部基准、因为 R42 已移除、但 PHI 板关闭、我需要重新连接 USB 才能再次供电...

尊敬的 Enrico:

我还在研究这个问题。 可能需要注意的是、ADC128S102 在 VD 与 VA 之间有一个二极管。 如果 VD 在 VA 未受电的情况下供电、则 VA 可能会反向供电、其压降为 0.7V(相对于 VD)。

这也适用于数字和模拟输入。 如果在器件上电之前输入端存在电压、则器件可能会反向供电并意外运行。 在我最近执行的一些测试中、VA 被反向供电导致了一个问题...

我会不断研究这一点、以获得更重要的建议。

此致、

Joel

尊敬的 Enrico:

自此之后有任何发现? 测得的 2.4V 对我来说非常有用、因为它告诉我来自另一个引脚的 3.3V 电压是正向偏置内部二极管、从而导致~0.7V 压降。 电路板上是否有读数为 3.3V 的地方?

在电路板上、VD 由 D1 齐纳二极管钳位至 3.6V。 这也能解释为什么 VA 和 VD 短路会导致问题吗?

我还移除了从 DOUT 到 VD 的上拉电阻 R33。 这不是必需的、可以帮助隔离硬件问题。

RET_SCLK 网络对于与 PHI 一起运行是必需的、但如果在外部使用、则可以移除 R37。

我只需重点从器件中移除可能导致杂散泄漏路径的所有外设。

此致、

Joel

尊敬的 Joel:

请原谅我缺席。 目前我没有执行您建议的测试。 开发板是共享的、我没有访问权限。

但我可能有一些新闻、因为我的同事使用 FPGA 板和相同的 ADC128102EVM 板进行了一些测试。

他们发现 SPI 连接存在一些串扰问题、并解决了在所有电缆长度上添加屏蔽层的问题。 行为与我在设置中遇到的行为相同。

下周我想我可以做一些测试。

谢谢。此致、

Enrico