Other Parts Discussed in Thread: DAC39J84, LMK04828

主题: LMK04828 中讨论的其他器件

工具/软件:

您好、

当我尝试配置 DAC39J84 时、我观察了同步信号

TX_tREADY 信号正在切换。 我要使用以下设置配置 DAC:

采样率= 500MHz 、

线路速率 = 5GSPS、

DACCLK = 500MHz 、

JESD Ref clk = 125MHz 、

SYSREF = 1.953125MHz 、

LMFS = 8411、

k = 32

FPGA 的器件时钟和 SYSREF 由 LMK04828 给出。 器件时钟

DAC (DACCLK) 由 HMC835 的 LO1 输出提供。 HMC835 的 LO2 输出为

该分频器的频率与 LO1 分频器的频率相同、DAC SYSREF 通过该分频器设置

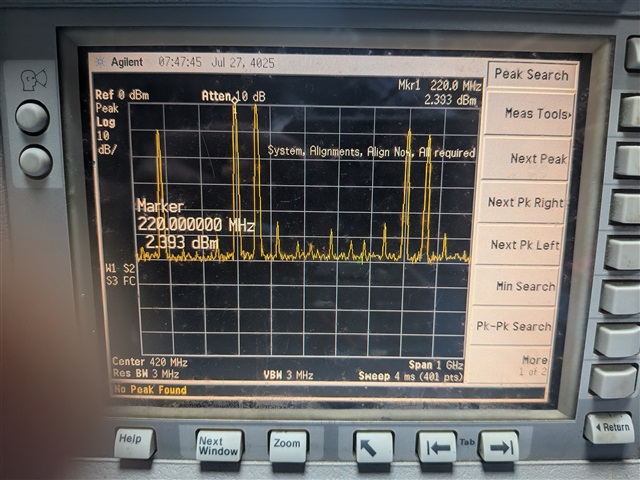

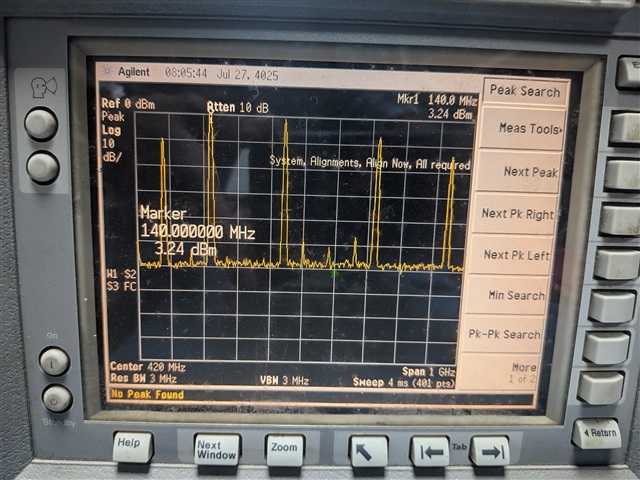

偏移量电压。 我对 SYSREF 执行了 NCO 测试、并观察到 SYSREF 正在

例如、我可以观察到多个峰值。

写入以下寄存器以配置 DAC -

ADDR 数据

0x00 0x001C

0x01 0x0800

0x02 0x2082

0x03 0xF080

0x04 0x00FF

0x05 0xFF0D

0x06 0xFFFF

0x07 0x0000

0x08 0x0000

0x09 0x0000

0x0A 0x0000

0x0B 0x0000

0x0C 0x0400

0x0D 0x0400

0x0E 0x0400

0x0F 0x0400

0x10 0x0000

0x11 0x0000

0x12 0x7000

0x13 0x7000

0x14 0x0000

0x15 0x0000

0x16 0x4000

0x17 0x0000

0x18 0x0000

0x19 0x4000

0x1A 0x0020

0x1b 0x0000

0x1E 0x1111

0x1F 0x99C0

0x20 0x8888

0x22 0x11B

0x23 0x01FF

0x24 0x0020

0x25 0x2000

0x26 0x0000

0x2D 0x0001

0x2E 0xFFFF

0x2F 0x0004

0x30 0x0000

0x31 0x7030

0x32 0x0700

0x33 0x7FC8

0x34 0x0000

0x3B 0x0800

0x3C 0x9028

0x3D 0x0088

0x3e 0x0108

0x3F 0x0000

0x46 0x0044

0x47 0x190A

0x48 0x31C3

0x49 0x5500

0x4A 0xFF1E

0x4B 0x1F00

0x4C 0x1F07

0x4D 0x0300

0x4E 0x0F6F

0x4F 0x1CC1

0x50 0x0000

0x51 0x00DF

0x52 0x00DF

0x53 0x0000

0x54 0x00FF

0x55 0x00FF

0x56 0x0000

0x57 0x00FF

0x58 0x00FF

0x59 0x0000

0x5A 0x00FF

0x5B 0x00FF

0x5C 0x1155

0x5E 0x0000

0x5F 0x0123

0x60 0x4567

0x61 0x0003

0x64 0x0000

0x65 0x0000

0x66 0x0000

0x67 0x0000

0x68 0x0000

0x69 0x0000

0x6A 0x0000

0x6B 0x0000

0x6C 0x0000

0x6D 0x0000

0x6E 0x6A70

0x6F 0x0325

0x70 0x076F

0x71 0x01D6

0x72 0x016E

0x73 0x5974

0x74 0xD6D8

0x75 0x7000

0x76 0x6A70

0x77 0x0325

0x78 0x076F

0x79 0x01D6

0x7A 0x016E

0x7B 0x5974

0x7C 0xD6D8

0x7D 0x7000

0x7E 0x0000

0x7f 0x0000

通过这些设置、我可以观察到 SYNC 和 READY 信号正在切换。 我已经验证过

数据表中“初始化设置“部分下提到的所有寄存器。 有任何寄存器

需要配置的设置或建立稳定链路需要考虑的任何其他设置?

此致

P. Anirudh Reddy