工具/软件:

您好、

我们在我们的工程中使用 DAC121C081、现在请告知 对于该芯片上的高速 (3.4MHz) 模式电路是否有任何重要影响?

我们目前面临的问题是、在特殊情况下调整 I2C 输入可能会导致芯片在刷新数万次后无输出。

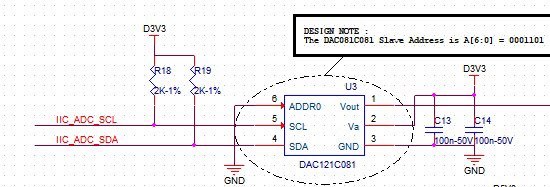

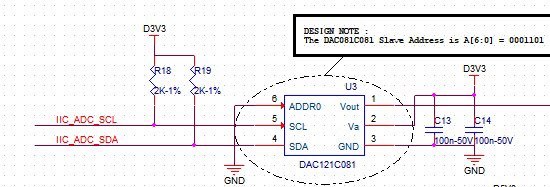

下面是我们的原理图?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好、

我们在我们的工程中使用 DAC121C081、现在请告知 对于该芯片上的高速 (3.4MHz) 模式电路是否有任何重要影响?

我们目前面临的问题是、在特殊情况下调整 I2C 输入可能会导致芯片在刷新数万次后无输出。

下面是我们的原理图?

Zhang、

除了 Paul 的注释外、您还应检查器件是否已进入高速模式。 对于 I2C 高速 (HS) 模式、需要首先发送控制器代码以确保器件为 Hs 模式做好准备。 之后、您应该能够在 Hs 模式下进行接收和发送。

您能否展示 Hs 模式下的发送和接收的示波器图? 一旦器件在 Hs 模式下接收并发送回数据、您需要确保微控制器不发送停止条件。 停止条件将使器件退出 Hs 模式并且器件返回快速模式。 在微控制器发送 Hs 模式后、您可能会丢失通信。

理想情况下、您可以使用逻辑分析仪检查与器件的所有通信、但示波器可能会起作用。

Joseph Wu

Zhang、

在图中、SDA 线路的上升时间似乎有点慢。 在 DAC121C081 中、VIH 电平为 0.7* VDD。 在此图中、VDD 看起来约为 3.3V、这意味着 SDA 需要达到 2.31V、以确保输入被视为有效高电平。

为了使 SDA 更快、您需要更高电流的上拉电阻、这可能意味着 2kΩ 上 拉电阻太小、并且 1.1kΩ 上拉电阻提供足够的电流来更快地上拉节点。 如果可以减小总线上的电容值(尽管很大的总线电容是寄生的并且来自电路板的布局布线)、则可以保留 2kΩ 电阻器。

我们通过 以下链接(I2C 基本指南)获得了有关 I2C 的应用手册: https://www.ti.com/lit/pdf/sbaa565

应用手册第 25 页简要介绍了电气特性。 最后、从第 28 页开始简要讨论上拉电阻器的大小。

Joseph Wu