请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADC3544工具/软件:

您好、我尝试设置 DDR 并行 14 位复数抽取输出、使 I 和 Q 分量分别在上升沿和下降沿输出、如数据表的图 8-30 所示。 当使用以下寄存器写入将输出设置为非抽取 SDR 时、我能够使用斜坡模式测试输出:

//将输出设置为并行 SDR

writeToReg (0x07、0xC8);

writeToReg (0x13、0x01);

延迟 (10);

writeToReg (0x13、0x00);

//选择 14 位输出

writeToReg (0x1B、0x10);

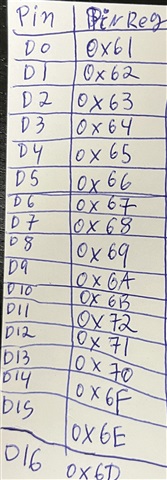

// 14 位引脚位映射

writeToReg (0x46、0x6D);//引脚 20 ->位 13

writeToReg (0x47、0x6C);//引脚 21 ->位 12

writeToReg (0x48、0x67);//引脚 22 ->位 11

writeToReg (0x49、0x66);//引脚 23 ->位 11

writeToReg (0x4A、0x65);//引脚 24 ->位 9

writeToReg (0x43、0x64);//引脚 27 ->位 8

writeToReg (0x42、0x5F);//引脚 28 ->位 7

writeToReg (0x41、0x5E);//引脚 29 ->位 6

writeToReg (0x40、0x5D);//引脚 30 ->位 5

writeToReg (0x3F、0x5C);//引脚 32 ->位 4

writeToReg (0x3E、0x57);//引脚 33 ->位 3

writeToReg (0x3D、0x56);//引脚 34 ->位 2

writeToReg (0x3C、0x55);//引脚 35 ->位 1

writeToReg (0x3B、0x54);//引脚 36 ->位 0

//斜坡测试模式

writeToReg (0x14、0b10000);

writeToReg (0x15、0x0);

writeToReg (0x16、0b1000);

此代码生成以二进制表示的预期计数方式 1。

但是、当我将第一次寄存器写入更改为 A9(DDR 输出)时、输出数据变为行话、许多位看起来未使用、如下面的简短输出部分所示:

这些位之所以反转、是因为某种原因、只有 5 个最高位发生变化、最高位每 4 个输出发生变化、中间位仅为零、LSB 应该不改变的值始终为 101。

数据表的图 8-30 看起来所有位都是并行输出的、但图 8-38 似乎表明、每次 DCLK 变化只有一半的位是输出。

任何帮助我修复我的设置将非常感谢。

谢谢您、

Felipe