Other Parts Discussed in Thread: ADS131M04

您好团队:

我附上了从具有 ADC 同步和不具有 ADC 同步的 ADC 通道 0 捕获的原始样本。

如果每 5ms 定期同步一次 ADC、我会看到一些数据损坏。 请帮助我解决 issue.WithADCSync.txtWithoutADCSync.txt 的问题

此外、同步 ADC 第 1 次采样延迟后、我已在下面调整了刮擦。

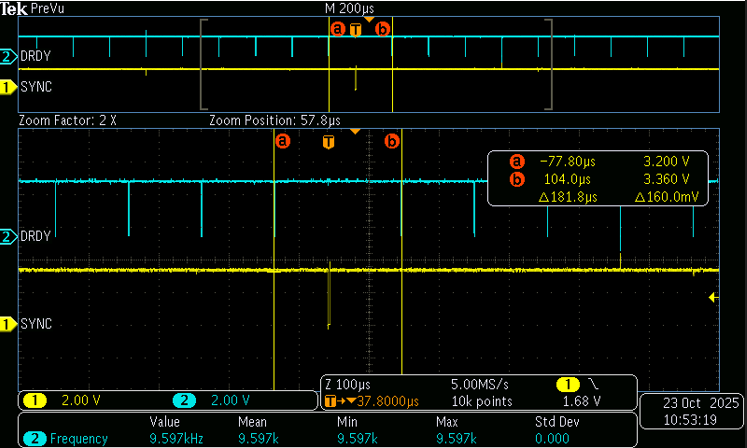

同步后从 DRDY 到第一个 DRDY 的时间差为 181.8uS

从 Sync 到第 1 个 DRDY 以及之后的数据速率与我保留的 IE 104us 相同。

如何在不影响/破坏任何样本数据的情况下管理同步后第一个样本的数据速率变化?

谢谢

BR、

Shraddha N.