Other Parts Discussed in Thread: DAC8760, DAC8775, DAC7750

主题中讨论的其他器件: DAC8775、 DAC7750

工具/软件:

尊敬的技术支持团队:

问题 1

常见问题解答。

当模拟电源是单个 15V 电源并且使用 0-5V/0-10V/4 –20mA 时、它是否可以在接近 0V 时输出电压而没有任何问题?

电源下余量中列出的 AVSS 是否必须设置为–0.5V 或更低?

问题 2

在 ESD 容差方面、HBM 的性能是±1.5kV、这是仅使用任何保护元件时的性能吗?

或者、这是否意味着组装数据表 9.2 中所列的电路时的容差?

问题 3

数据表中的各种规格都是在 Vref 和 DVDD 由外部供电的条件下指定的、但是当使用内部生成的 Vref 和 DVDD 时、规格如何变化?

请提供关于 TUE 的信息。

问题 4

关于短路电流的说明、电气特性中描述了典型值、但 Ta = 25℃ 时最差值(最小值,最大值)是多少?

问题 5.

还提供了 REFOUT 和 DVDD 的短路电流说明、但您也有这些的温度特性吗?

问题 6.

未使用 Vout 时的输出阻抗是多少?

问题 7

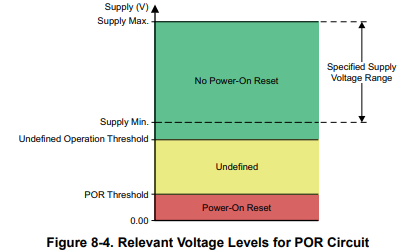

8.3.7 上电复位、当 RESET 检测电压降至低于 RESET 检测电压的时间超过 1ms 时、是否有关于复位的说明?

达到复位电压后、取消复位需要多长时间?

问题 7

我无法找到对电流输出允许的负载电阻的任何描述、但认为满足顺从电压的条件限制值是允许的负载电阻是正确的吗?

问题 8.

不使用 Iout 时、您是否有关于 Iout 的漏电流的任何信息?

问题 9.

您是否有关于 内部生成的 DVDD = 4.6V 的精度和温度特性的任何信息?

问题 10.

我从数据表的表 7.5 中知道、使用内部 DVDD 时电流消耗 AIDD 大约会增加 1mA、但使用内部 Vref 时电流消耗会增加多少?

此致、

TTD