Other Parts Discussed in Thread: DAC39RF12EVM

尊敬的团队:

代表我们的客户发帖。

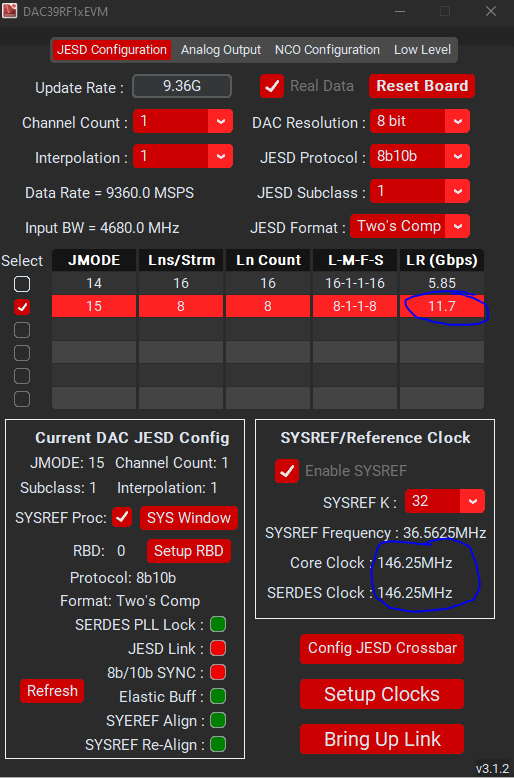

我使用 DAC39RF1xEVM GUI 在 DAC39RF12EVM 上设置时钟和寄存器。 当我跟随 AMD 时 JESD204C v4.3 LogiCORE IP 产品指南 (PG242) 规范文档指出、对于 JESD 协议 8b10b、时钟频率应为串行线速率除以 40。 当我尝试设置 11.7Gbps 的串行线路速率时、内核时钟应为 292.5MHz、但您的 GUI 似乎会将其设置为 146.25MHz。 它基本上是取线速除以 80。 您能否确认正确设置此项、以及它是否适用于以相同线路速率通信但使用 292.5MHz FPGA 时钟运行的 Xilinx FPGA?

此致、

Danilo