Other Parts Discussed in Thread: DAC38RF82

您好、TI 专家、

我正在定制电路板上进行 DAC38RF82 调试、可能会得到您的支持吗?

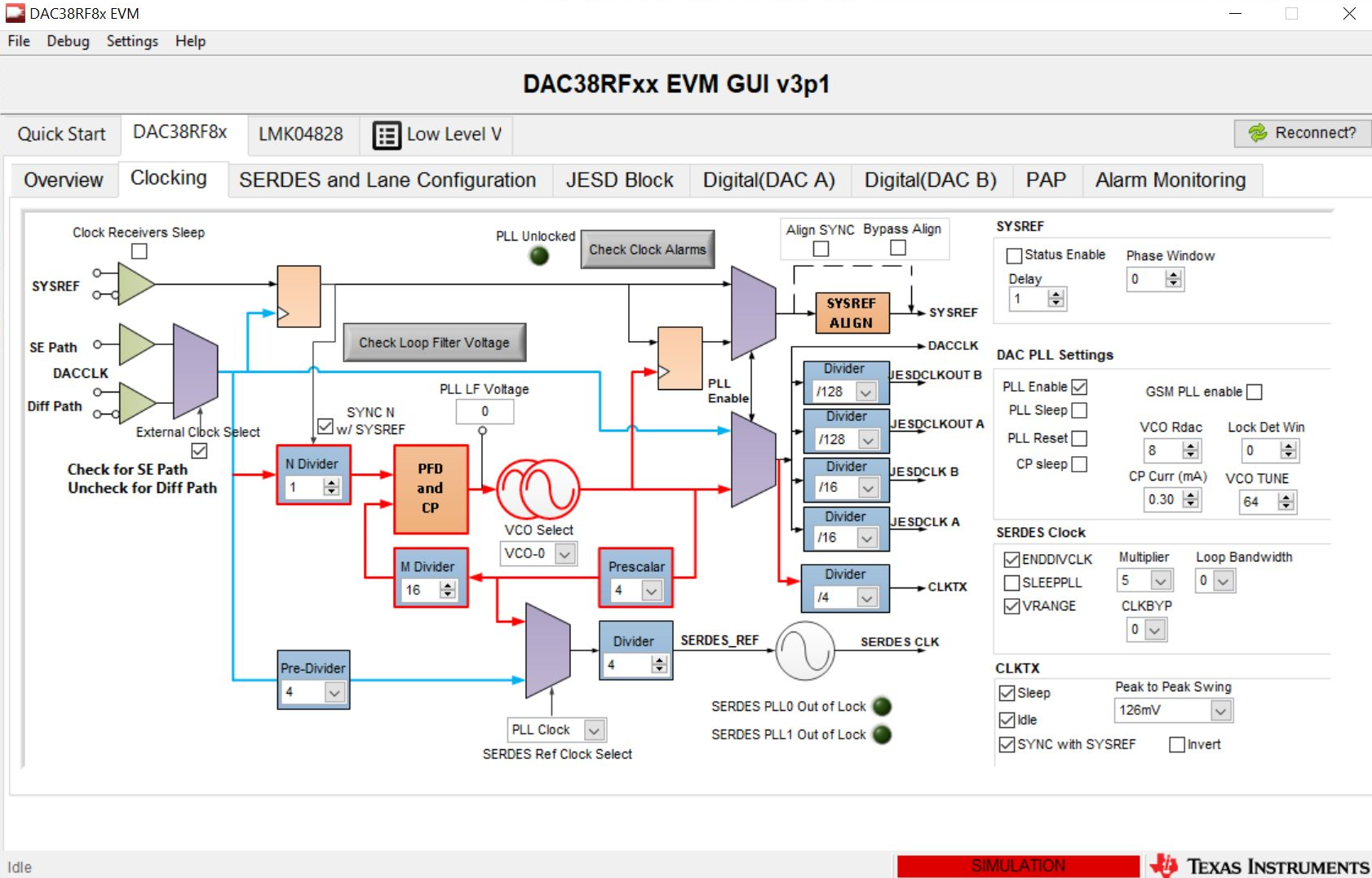

1、我的第一个问题是关于 EVM GUI 软件、我只能启动如下所示的“概述表“、

但我确实发现论坛中其他人的 GUI 包含如下几个工作表(相同的仿真模式)

我尝试了 Win 10 和 Win 11 操作系统、这是相同的情况、对此问题有任何建议吗?

2、我们设计这个 DAC 以 9GHz 采样率、8 位模式运行、DAC 引脚上的参考频率为 1.2GHz、来自外部 PLL(使用示波器检查它是否有良好的 SI)、但我无法获取 DAC PLL 锁定 (DAC 寄存器 0x05=07)、也没有来自 DAC 的射频输出、已执行以下操作:

1) 已检查电源轨正常、RESET 和 TXEN 引脚是否为高电平。

2) 探测 10nF 交流电容器后的时钟、靠近 DAC CLK 引脚、其 1.2GHz 并具有良好的 SI。

3) 运行初始配置代码、读出 0x7F[15:10]=10000b、然后将 VCO 值(寄存器 0x433[14:8]从 0 调整为 127)、但 PLL_LFVOLT(寄存器 0x06[7:5])始终保持为 0。

4) 与 PLL 相关的寄存器设置为:

| 链接 | 寄存器 | 数据值 |

| 4. | a. | 7003. |

| 4. | b. | 0 |

| 4. | 23 | FC00 |

| 4. | 31. | 0438 |

| 4. | 32 | E08 |

| 4. | 33 | FF3C |

| 4. | 3b. | 9800 |

| 4. | 3c. | 9029 |

| 4. | 3e. | 8909. |

经过长时间的挣扎,几乎没有线索从我的想法现在,谢谢你的帮助提前!