Other Parts Discussed in Thread: ADC3564, ADC3664-SP, LMK04832

器件型号: ADC3564

主题中讨论的其他器件: ADC3664-SP、 LMK04832

您好、

我目前正在处理的 ADC3564 并且对其配置和行为有一些顾虑。 感谢您对以下几点的见解:

-

2 线 16 位模式下的位映射

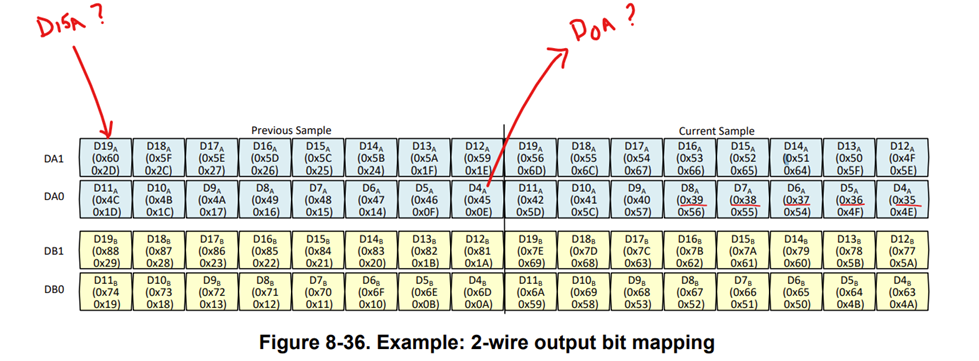

在当前设置中、我使用 2 线 16 位接口。 我想确认位映射是否始终存在 MSB 对齐 (即 Data[19:4])或如果可以使用 数据[15:0] 相反、这意味着 D4A 对应于 D0A 和 D19A 到 D15A。

假设顺序保持不变 (DA1:MSB、DA0:LSB)、我是否可以遵循此备用映射? 例如、在这种情况下、D0A 的地址将0x43用于上一个样本(而不是)0x45、而0x39用于当前样本(而不是,数据表将其列为)0x3B0x35。 您能否澄清一下这一解释是否有效? -

解决数据表中的范围拼写错误?

在上述示例中、0x35DA0 的地址似乎超出了信道 A 的有效范围、即0x39至0x60。 您能否确认0x35数据表中是否有拼写错误? -

DLCKIN 与采样时钟 — 异步域

最大功耗 采样时钟 直接馈送到 ADC、而 DCLKIN 是使用不同的基准时钟通过 FPGA 内部的 MMCM 生成的。 由于这些时钟不是源同步的、我担心 ADC 如何处理此类异步域。

您是否有管理此类设置的建议或最佳实践? -

寄存器 0x09 用于 2 线 16 位接口的配置

寄存器应该0x09保持在默认值 (0x00)、还是需要切换位[2]并[3]在 2 线 16 位模式下正常运行?我知道这些似乎很细微、但由于数据表中存在多种不一致之处、我正在设计阶段早期尝试解决这些问题。 我还在 AMD 社区中遇到了一些关于这款芯片的负面反馈——有人称这是“与 FPGA 连接太可怕了“——但我更喜欢依靠事实和正确的理解而不是意见。

提前感谢您的支持。

此致、

Sourav