器件型号: ADC3544

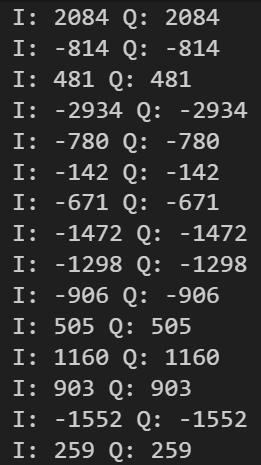

大家好、我尝试使用 DDR 并行复数抽取输出获取 IQ 数据、但上升沿和下降沿的输出都是相同的。 下面是一个噪声数据片段、该数据被解释为 int16 时收集:

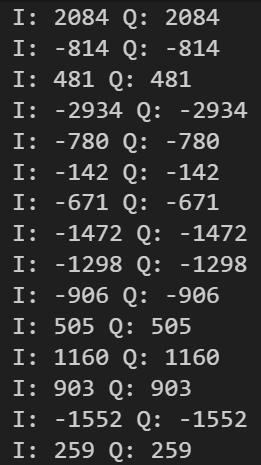

以下是我发送到 ADC 的设置命令:

当 I 输入波形时、同相分量的输出看起来符合预期、但当然无法在正交分量的情况下正确处理信号。 任何帮助都将非常感谢。

谢谢、

Felipe

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

器件型号: ADC3544

大家好、我尝试使用 DDR 并行复数抽取输出获取 IQ 数据、但上升沿和下降沿的输出都是相同的。 下面是一个噪声数据片段、该数据被解释为 int16 时收集:

以下是我发送到 ADC 的设置命令:

当 I 输入波形时、同相分量的输出看起来符合预期、但当然无法在正交分量的情况下正确处理信号。 任何帮助都将非常感谢。

谢谢、

Felipe