Other Parts Discussed in Thread: AFE5832LP

器件型号: AFE5832LP

我要将 AFE5832LP 设置为测试模式斜坡、通过 FPGA 从 32 个通道接收 AD 数据、并检查更改模式。 我已确定以下问题:

1:通道 1 至 16 的变化与预期的斜坡模式一致。

2:通道 17 至 32 的变化与预期的斜坡模式一致。

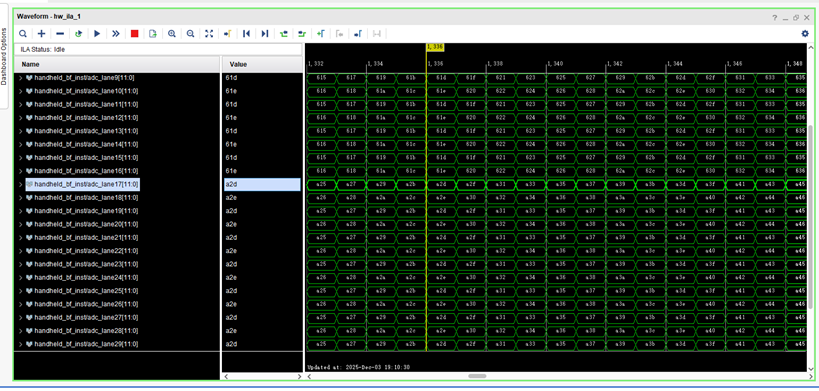

3:但是、第 1 组至第 16 组和第 17 组至第 32 组的数据变化不一致、如下图所示:

1.测试模式寄存器配置方法:

1:将寄存器 0x02 设置为 0x0380

2:将寄存器 0x04 设置为 0X0018

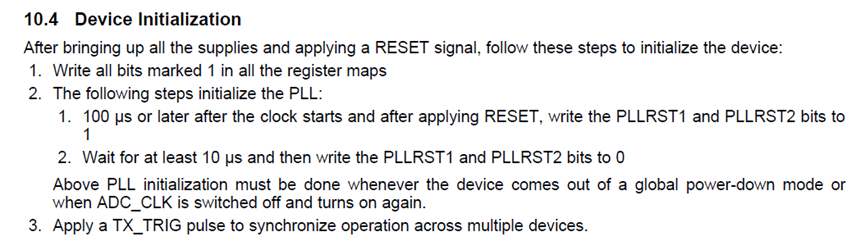

2.芯片复位过程

在重置过程中、请严格验证手动要求

1:重置完成、等待 120us>100us

2:复位 PLLRST1 和 PLLRST2 后、等待 12us>10us

3:PLLRST1 和 PPLRST2 复位完成后、等待 100N 并发送四个宽度为 80MHz 的高电平 TX_TRIG 信号

3. FPGA 接收设置

由于是 AFE5832LP、16 个 LVDS 通道组合在一起、16 个 LVDS 设置完全相同。