Other Parts Discussed in Thread: AFE58JD48, AFE58JD28

《Thread: Test》(线程:测试)中讨论的其它部件 ,AFE58JD28

尊敬的支持:

现在,我正在使用 FPGA (XCKU3P)接收来自 AFE58JD48至 JESD204B 的采样数据。

AFE 配置为 JESD 160X 模式,Subclass2,16bit-30MHz 采样率,由 SPI 根据以下过程配置:

0x12 0x000A //PAGE_SEL_8CH_DIG1,PAGE_SEL_8CH_DIG2 = 1

0x31 0x00C0 //PLL 模式= 160X,CTRL_K=1,CTRL_MODE = 1.

0x32 0x8000 //EN_1L_MODE0 = 1.

0x34 0x1107 //JESD_subclass = 2,JESD_version = 1,K = 8

0x35 0x00C0 //L=1,CTRL_L = 1,CTRL_M = 1

0x36 0x0003 //M = 4

0x5D 0x8000 //EN_1L_MODE1 = 1.

0x2C 0x0008 //EN_1L_Mode2 = 1.

0x30 0x8002 //启用 Mux PDN。 MUX_PDN_3_4;在 LAN2上引入 Lane3;PDN JESD2 (用于顶级 ADC)

0x30 0x8006 //Mux_PDN_5_6;在 LANe8上使用 LANe5;PDN JESD1 (用于底部 ADC)

0x12 0x0000 //禁用页面选择

0x12 0x0002 //page_sel_8CH_DIG1 =1,选择前8个通道

0x5F 0x00A0 //PDN Lane 2

0x12 0x0008 //page_sel_8CH_DIG2 =1,选择底部8通道

0x65 0x0050 //PDN Lane 7

0x12 0x0000 //禁用页面选择

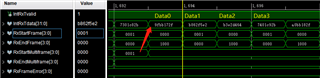

FPGA 固件使用 Xilinx IP JESD204(7.2),单通道,8-F,8-K,4.8Gbps-LineRate。

位文件将生成并下载到 FPGA,Rx_data 将通过 ILA 获取。 我想知道如何将 Rx_data 转换为每个通道的采样数据。