哈洛每个人,

我 需要连接 ADS9110。 我们的硬件开发人员按照第章中所述为 ADC 布线 7.5.4.2.(单设备:标准 SPI 接口的最小引脚)

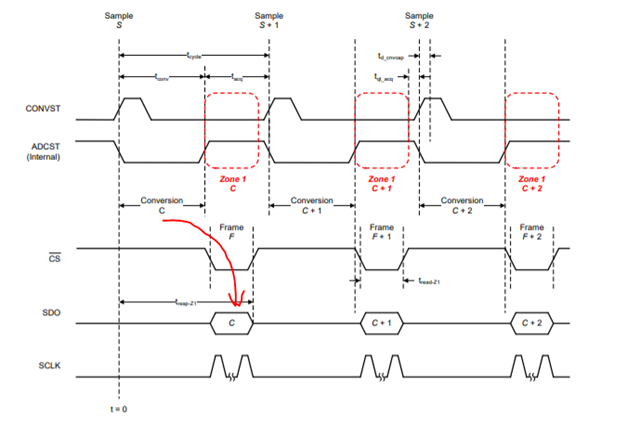

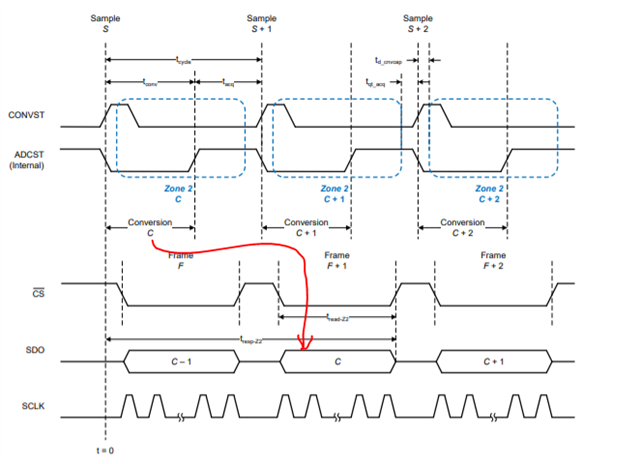

但是,阅读第7.5.2章(交错转换周期和数据传输帧)时,人们指出:

'要达到额定性能规格,主机控制器必须确保数字信号不会发生切换

在静默采集时间(TQT_ACQ)和静默孔径时间(TD_cnvcap)[...]"

此外,本章中的所有计时图都表明,CS 在 TD_cnvcap 之后会变低。

CS 和 CONVST 之间的连接是否违反了此规则?

连接 CS 和 CONVST 时,性能会有什么影响?

谢谢,此致,

马塞尔。