Other Parts Discussed in Thread: ADC09QJ1300EVM

“线程: 测试”中讨论的其它部件

您好,专家,

我的客户遇到 ADC09QJ1300EVM 输出振幅不足的问题。

测试条件1 (无问题)

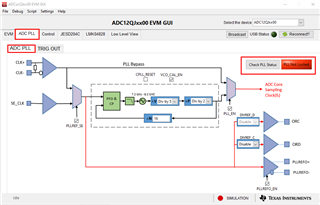

GUI:板载50M Ref,FS=500Msps,JMODE10

Rx_DIV = 16,32和64

输出振幅为460mV @RX_DIV=16 (195.3MHz)

输出 振幅为 540mV @RX_DIV=32 (97.7MHz)

输出 振幅为530mV @RX_DIV=64 (48.8MHz)

测试条件2 (问题)

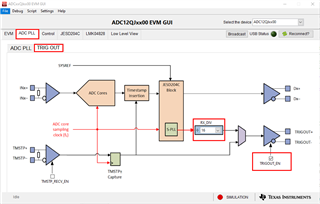

GUI:板载50M Ref,FS=800Msps,JMODE10

Rx_DIV = 16,32和64

输出 振幅为280mV @RX_DIV=16 (312.5MHz)

输出 振幅为380mV @RX_DIV=32 (156.25MHz)

输出 振幅为340mV @RX_DIV=64 (78.125MHz)

*它是规格输出 V diff (最小) 400m Vpp-diff

在 这种测试条件下,FPGA 未锁定 PLL。

测量点

R234 (DNP) J9 TRIGOUT+侧和 R241 (DNP) K9 RTIGOUT-侧

请告诉我你的建议。

谢谢

穆克