你好!

我正在执行一个项目,需要将高速 ADC (ADC12DJ5200RFEVM)连接到 FPGA (VCU118)。 系统可能如下所示:

ADC ->(FMC)-> FPGA。

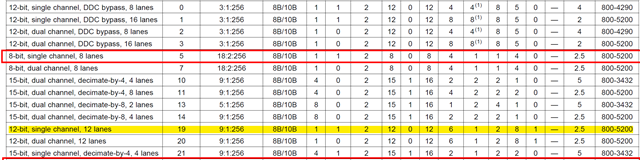

我需要将 ADC 采样的12位宽数据从通道 A 的10Gsps 从 ADC 传输到 FPGA,因此我选择使用 JMOD19模式。

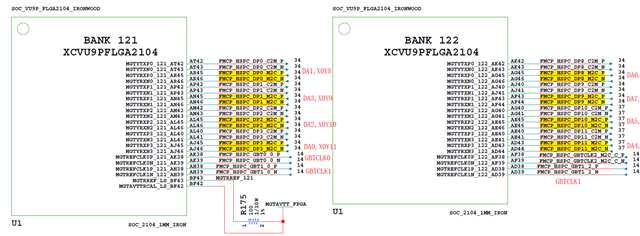

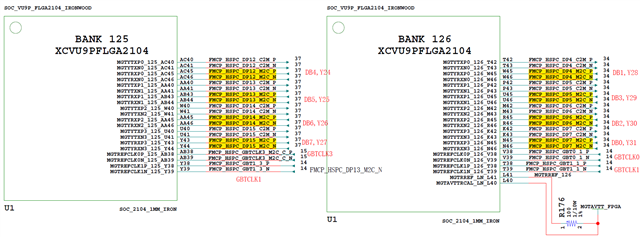

ADC 具有链路 A 和链路 B,它们对应于 VCU118上的 BANK121 (链路 A),BANK122 (链路 A),BANK125 (链路 B)和 BANK126 (链路 B)。 此外,VU9P 的 SLR0中有121号银行和122号银行, VU9P 的 SLR1中有125号银行和126号银行。 SLR 是 VU9P 的 SLR (超级逻辑区域)。

在每个链路中,我使用两个 jesd204 PHY 核心和一个 jesd204核心,两个 PHY 核心共享一个 REFCLK (参考时钟)。

调试结果时,从链路 A 收到的结果是正确的。 相反,从链路 B 收到的结果是错误的。

我发现线路对齐是 K28 5,两者之间没有区别,但在 ILAS 阶段,两个链路 PHY 核心的数据输出是不同的。

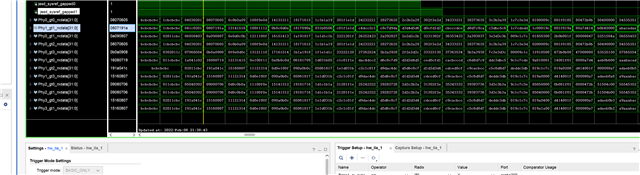

在 ILAS 阶段,第一个多帧应该是增量计数器。 链路 A 的 PHY 核心输出(py0_gt0_rxdata)正确,链路 B 的 PHY 核心输出(py1_gt1_rxdata)错误。