“线程: LMK04828, 测试”中讨论的其它部件

您好,球队,

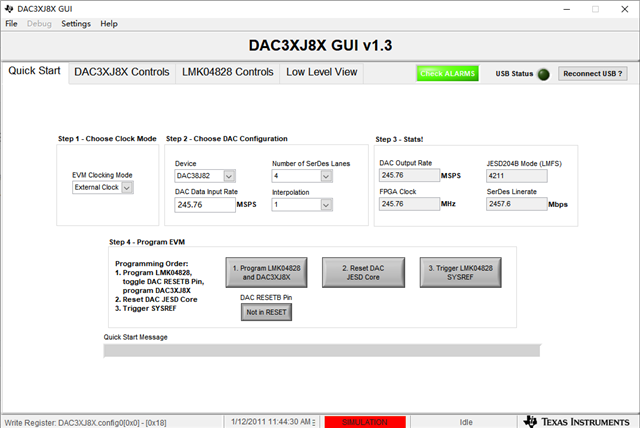

当我们的一个客户使用 DAC38J82 进行开发时,在配置参数后 Serdes PLL 无法锁定,FIFO 报告了错误;

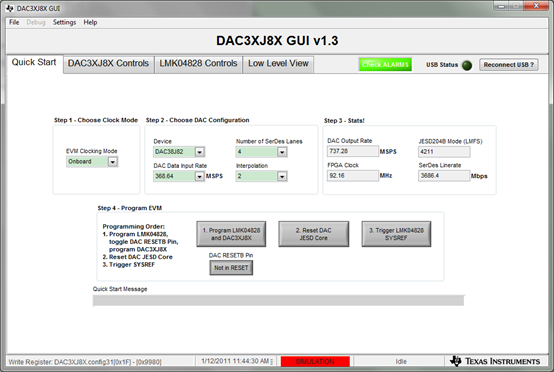

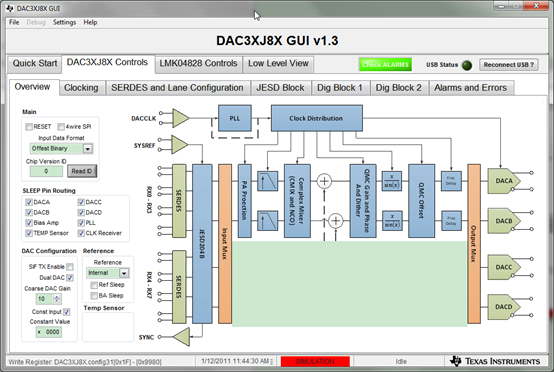

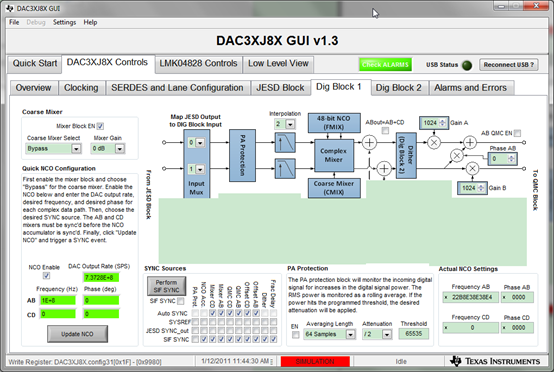

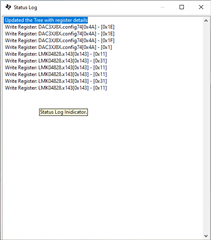

客户使用 DAC3XJ8X GUI v1.3 软件生成所需的参数。 生成参数后未进行任何更改。 参数配置如下图所示。

LMK04828

0x00 0x00

0x02 0x00

0x100 0x01

0x101 0x55

0x103 0x00

0x104 0x20

0x105 0x00

0x106 0xF0

0x107 0x11

0x108 0x61

0x109 0x55

0x10B 0x01

0x10C 0x20

0x10D 0x00

0x10E 0xF0

0x10F 0x76

0x110 0x08

0x111 0x55

0x113 0x00

0x114 0x00

0x115 0x00

0x116 0xF9

0x117 0x00

0x118 0x18

0x119 0x55

0x11B 0x00

0x11C 0x20

0x11D 0x00

0x11E 0xF9

0x11F 0x00

0x120 0x10

0x121 0x55

0x123 0x00

0x124 0x00

0x125 0x00

0x126 0xF9

0x127 0x11

0x128 0x08

0x129 0x55

0x12B 0x00

0x12C 0x00

0x12D 0x00

0x12E 0xF9

0x12F 0x00

0x130 0x08

0x131 0x55

0x133 0x00

0x134 0x20

0x135 0x00

0x136 0xF9

0x137 0x01

0x138 0x40

0x139 0x02

0x13A 0x00

0x13B 0xA0

0x13C 0x00

0x13D 0x08

0x13E 0x03

0x13F 0x00

0x140 0x00

0x141 0x00

0x142 0x00

0x143 0x12

0x144 0xFF

0x145 0x00

0x146 0x10

0x147 0x12

0x148 0x02

0x149 0x42

0x14A 0x02

0x14B 0x16

0x14C 0x00

0x14D 0x00

0x14E 0xC0

0x14F 0x7F

0x150 0x03

0x151 0x02

0x152 0x00

0x153 0x00

0x154 0x78

0x155 0x00

0x156 0x78

0x157 0x00

0x158 0x96

0x159 0x00

0x15A 0x78

0x15B 0xF4

0x15C 0x20

0x15D 0x00

0x15E 0x00

0x15F 0x0B

0x160 0x00

0x161 0x01

0x162 0x44

0x163 0x00

0x164 0x00

0x165 0x0C

0x166 0x00

0x167 0x00

0x168 0x0C

0x169 0x5B

0x16A 0x20

0x16B 0x00

0x16C 0x00

0x16D 0x00

0x16E 0x13

0x17C 0x15

0x17D 0x0F

DAC_reset

0x00 0x1

DAC3XJ8X

0x00 0x0018

0x01 0x0003

0x02 0x2002

0x03 0xA300

0x04 0xF0F0

0x05 0xFF07

0x06 0xFFFF

0x07 0x3100

0x08 0x0000

0x09 0x0000

0x0A 0x0000

0x0B 0x0000

0x0C 0x0400

0x0D 0x0400

0x0E 0x0400

0x0F 0x0400

0x10 0x0000

0x11 0x0000

0x12 0x0000

0x13 0x0000

0x14 0x0000

0x15 0x0000

0x16 0x0000

0x17 0x0000

0x18 0x0000

0x19 0x0000

0x1A 0x0023

0x1b 0x0000

0x1E 0x9999

0x1f 0x9980

0x20 0x8008

0x22 0x1B1B

0x23 0x01FF

0x24 0x0020

0x25 0x2000

0x26 0x0000

0x2D 0x0001

0x2E 0xFFFF

0x2F 0x0004

0x30 0x0000

0x31 0x1000

0x32 0x0000

0x33 0x0000

0x34 0x0000

0x3B 0x0000

0x3C 0x0050

0x3D 0x0088

0x3E 0x0148

0x3F 0x0000

0x46 0x1882

0x47 0x01C8

0x48 0x3143

0x49 0x0000

0x4A 0x0F3E

0x4B 0x1200

0x4C 0x1303

0x4D 0x0100

0x4E 0x0F4F

0x4F 0x1C61

0x50 0x0000

0x51 0x00DC

0x52 0x00FF

0x53 0x0000

0x54 0x00FC

0x55 0x00FF

0x56 0x0000

0x57 0x00FF

0x58 0x00FF

0x59 0x0000

0x5A 0x00FF

0x5B 0x00FF

0x5C 0x1133

0x5E 0x0000

0x5F 0x3210

0x60 0x5764

0x61 0x0211

0x64 0x0001

0x65 0x0001

0x66 0x0001

0x67 0x0001

0x68 0x7709

0x69 0x0000

0x6A 0x0000

0x6B 0xBD07

0x6C 0x0007

0x6D 0x0090

0x6E 0x0000

0x6f 0x0000

0x70 0x0000

0x71 0x0000

0x72 0x0000

0x73 0x0000

0x74 0x0000

0x75 0x0000

0x76 0x0000

0x77 0x0000

0x78 0x0000

0x79 0x0000

0x7A 0x0000

0x7B 0x0000

0x7C 0x0000

0x7D 0x0000

此致,

罗艾米