您好,

欢迎您的到来!!

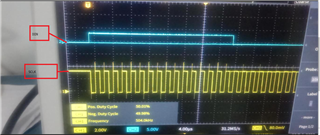

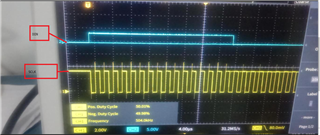

我正在将 ads1118与 FGPA 板(xc7a100t)连接,SPI 3线模式(cs 永久绑定到 GND),并配置寄存器的默认值。我正在尝试读取 ADC 通道0,输入为2.5V, 但我正在读-1.被测针脚总是很高,我附加了 DIN,SCLK CRO 结果。我有几个问题

1.是否要将 DOUT/DDRDY 配置为控制器端的中断引脚?

设备工作所需的最低时钟速度是多少?

3. 3线 SPI 模式是否适用于设备?

此致

阿杰

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,

欢迎您的到来!!

我正在将 ads1118与 FGPA 板(xc7a100t)连接,SPI 3线模式(cs 永久绑定到 GND),并配置寄存器的默认值。我正在尝试读取 ADC 通道0,输入为2.5V, 但我正在读-1.被测针脚总是很高,我附加了 DIN,SCLK CRO 结果。我有几个问题

1.是否要将 DOUT/DDRDY 配置为控制器端的中断引脚?

设备工作所需的最低时钟速度是多少?

3. 3线 SPI 模式是否适用于设备?

此致

阿杰

您好,Ajay,

SCLK 应低怠速,而不是高怠速,如您的示波器拍摄中所示。 ADS1118数据表的第9.5.3节中提到了这一点。 请先解决此问题,然后再执行其他操作。

您应该监视 DOUT/DDRY 引脚,以查看 DRDY 何时从高转换为低。 当您的控制器检测到这种情况时,您必须遵循数据表协议来检索数据(第9.5-7节)。

我不确定最低 SCLK 速度是多少,数据表中未定义此速度。 您希望在哪个 SCLK 上运行 ADC?

根据第9.5.1节,ADS1118可以在3线 SPI 模式下运行。

布莱恩

您好,Ajay,

我不知道您的控制器为什么要降低 SCLK 频率,但这不是 ADC 问题。

ADS1118在 SCLK 的下缘上超时数据。 这在您发送的最后一个逻辑分析器图解中是正确的。 但是,这一最新的逻辑分析器图解显示了上升边缘的数据超时。 请更正此问题,以便 ADS1118正确提供数据,

我建议仔细阅读数据表(9.5)的接口和数据检索部分,以便充分了解 ADS1118的工作原理。 该文档详细介绍了您遇到的许多问题。

布莱恩