“线程:测试”中讨论的其它部件

大家好,团队

我的客户需要帮助。

部件:ADS4449IZCR。

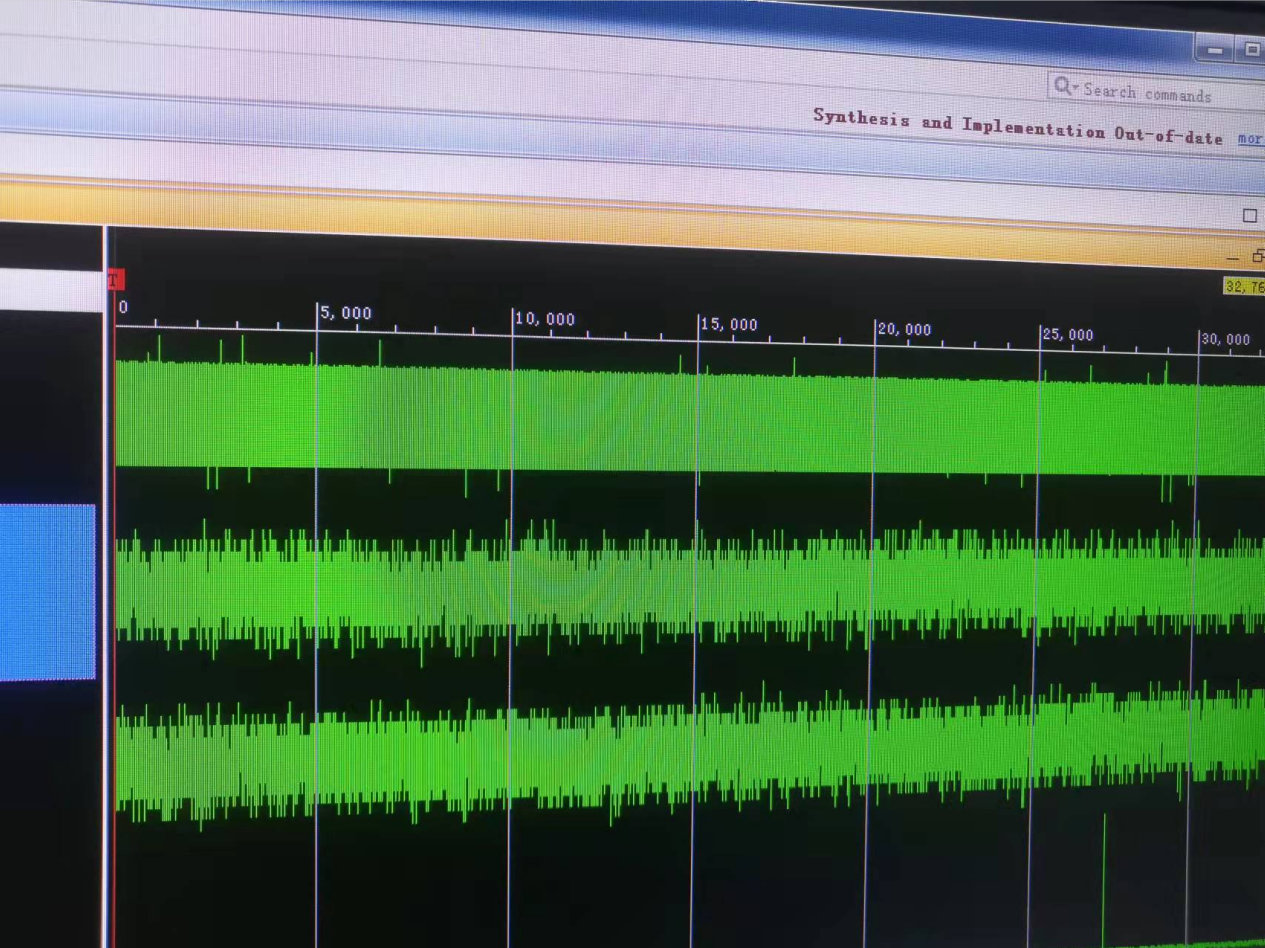

Vivadio 软件

广告采样后,它进入 FPGA 并通过 FPGA 捕获数据,

时间范围内有许多毛刺,噪音底部不稳定,杂散信号在频率范围内很大。

我想问,在什么情况下会导致这样的峰值,以及如何减少虚假信号

请帮帮我。 谢谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好,团队

我的客户需要帮助。

部件:ADS4449IZCR。

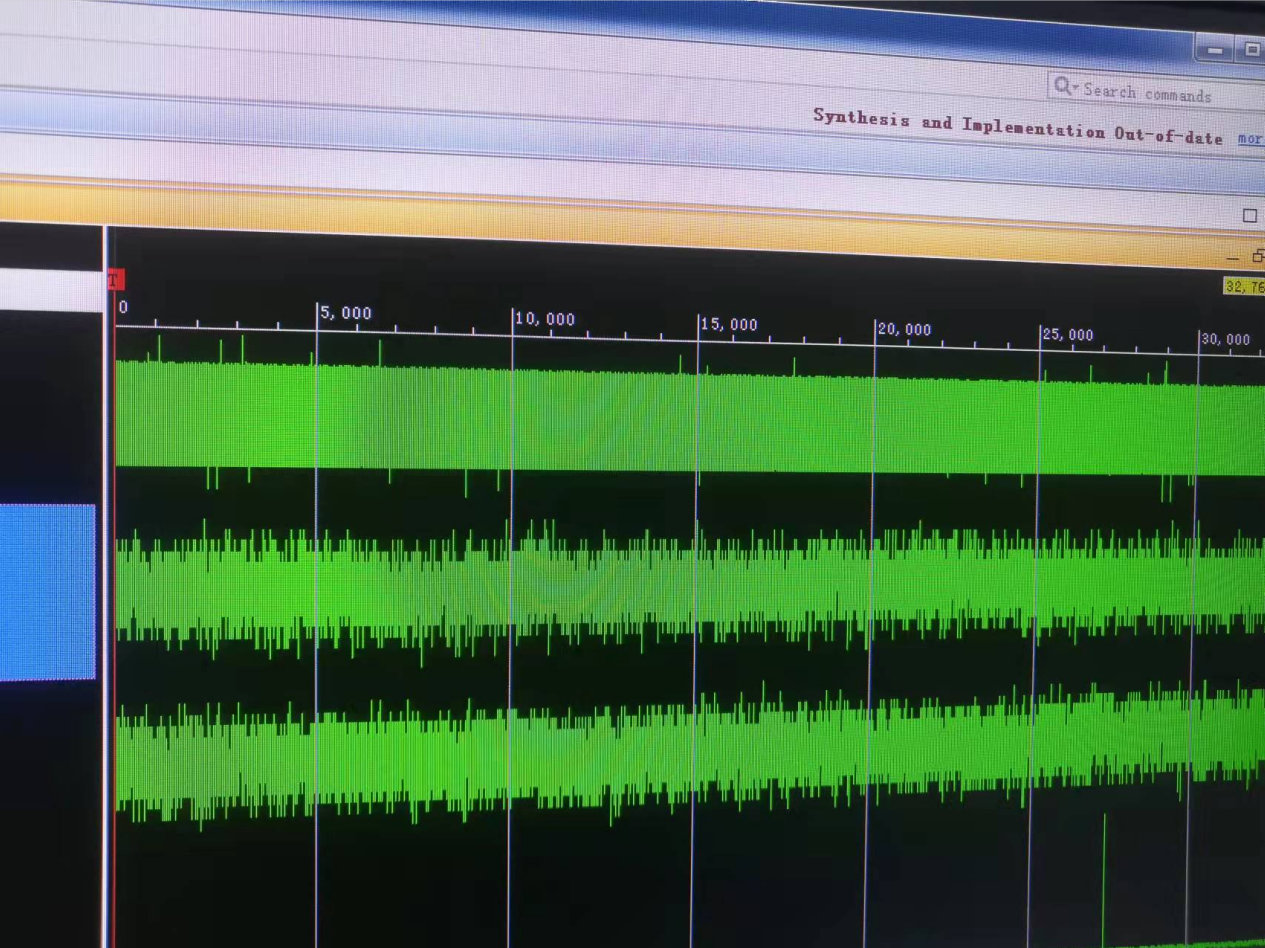

Vivadio 软件

广告采样后,它进入 FPGA 并通过 FPGA 捕获数据,

时间范围内有许多毛刺,噪音底部不稳定,杂散信号在频率范围内很大。

我想问,在什么情况下会导致这样的峰值,以及如何减少虚假信号

请帮帮我。 谢谢。