Other Parts Discussed in Thread: ADS131M06, ADS131M08EVM, AM2432

主题中讨论的其他部件: ADS131M08EVM, AM2432

您好,专家,

我正在阅读 ADS131M06的数据表。 我找到了以下关于SPI时钟和 调制器采样时钟的陈述。

| 8.3 5计时和电源模式 主时钟可以从外部获取到CLKIN引脚,也可以使用板载在内部生成 振荡器需要在XTAL1/CLKIN和XTAL2引脚之间连接晶体。 以获得最佳效果 性能,调制器采样时钟必须与串行数据时钟(SCLK)同步。 。 调制器采样时钟是从主时钟派生的,这意味着主时钟必须是同步的 使用SCLK。 因此,为了获得最佳性能,请为CLKIN提供主时钟,并确保数据检索正确 与CLKIN的时钟信号同步。 不使用时,关闭内部振荡器以节省电源。 |

这是否意味着CLCK和SCLK必须相同?

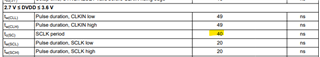

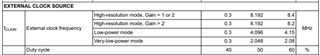

例如,我认为CLKIN=8.192MHz和 SCLK=20MHz (fyi,SPS 8K,OSR 512)可以工作,但根据数据表,这种组合似乎不起作用。

您能否分享您在这方面的知识,并澄清我的理解是否错误? 如果您共享两个时钟的最佳或推荐配置,我将不胜感激。

此致,

Moonil