我们设计了一个通过FMC-HPC将DAC3484与Xilinx FPGA接口的平台。 在这里,我们尝试以153.6MSPS速率将7MHz正弦波提供给所有四个通道(I0 Q0 I1 Q1),这些通道是从FPGA中的DDS生成的。

DACDATA_CLK为307.2 ,DAC_CLK为614.4 (插值为4)。DAC NCO配置为192MHz。 帧信号已用于同步FIFO源。NCO同步源为SIFSYNC。

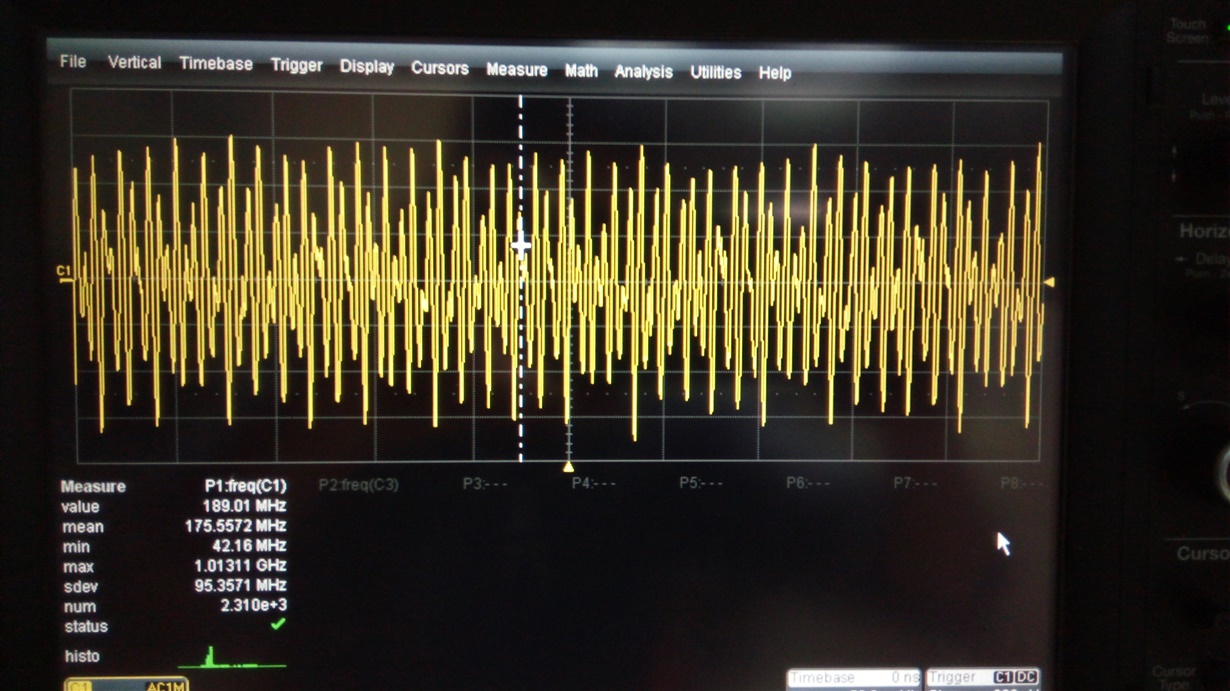

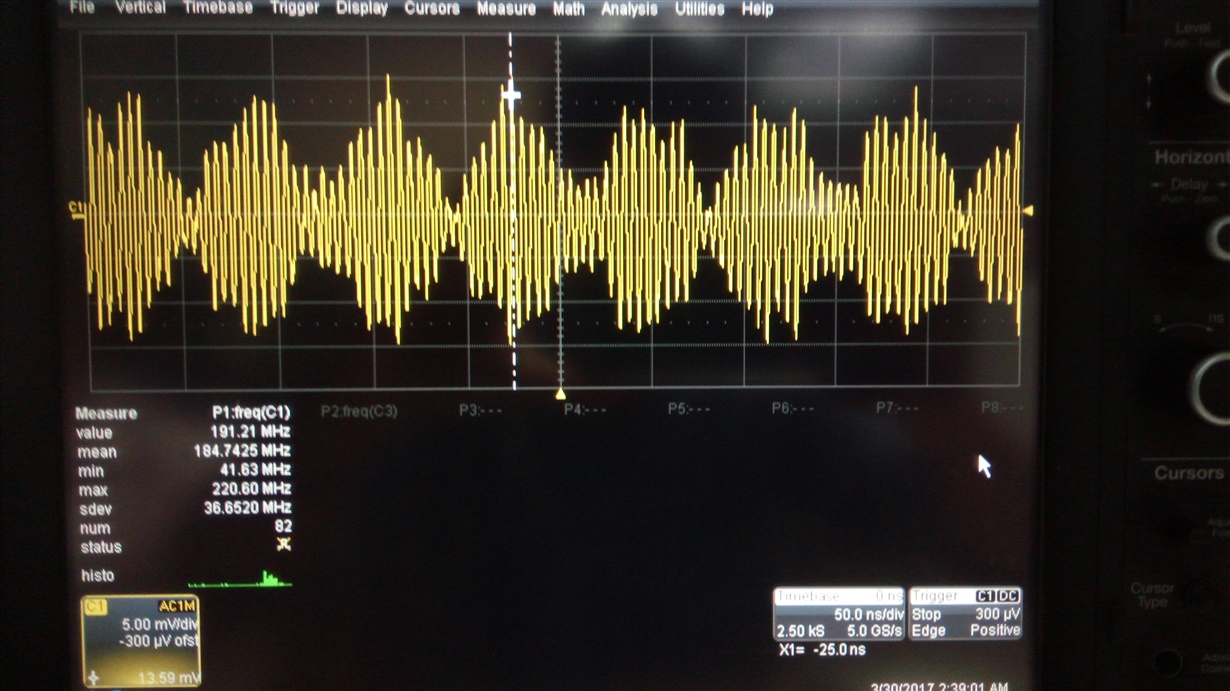

但我们观察到,在通道C-D的DAC输出上有两个频率为199MHz (192+7)和185MHz (192-7)的谐波,在通道A-B上有两个频率为199MHZ的谐波

这种行为的原因是什么?

再生器设置如下所示,

Cw0 <= x"00_028F";

Cw1 <= x"01_01";

CW2 <= x"02_80D2";--禁用混合器增益

CW3 <= x"03_D000";

Cw4 <= x"04_0000";

cw5 <= x"05_0000";

Cw6 <= x"06_3300";

cw7 <= x"07_FFFFFFFFF";

Cw8 <= x"08_0000";

cw9 <= x"09_8000";

cw10 <= x"0A_0000";

Cw11 <= x"0B_0000";

cw12 <= x"0C_0400";

Cw13 <= x"0D_0400";

CW14 <= x"0E_0400";

CW15 <= x"0F_0400";

CW16 <= x"10_0000";

cw17 <= x"11_0000";

cw18 <= x"12_0000";

cw19 <= x"13_0000";

cw20 <= x"14_0000";-- reg 0x14-0x17 if=192MHz

Cw21 <= x"15_5000";

cw22 <= x"16_0000";

cw23 <= x"17_5000";

cw24 <= x"18_2000";

Cw25 <= x"19_0000";

Cw26 <= x"1A_0020";

Cw27 <= x"1B_0800";

Cw28 <= x"1C_0000";

cw29 <= x"1D_0000";

Cw30 <= x"1E_1111";

Cw31 <= x"1F_8880";

Cw32 <= x"20_2201";

CW34 <= x"22_1B1B";

Cw35 <= x"23_FFFFFFFFF";

cw36 <= x"24_1800";

Cw37 <= x"25_7A7A";

Cw38 <= x"26_B6B6";

Cw39 <= x"27_EAA";

Cw40 <= x"28_4545";

Cw41 <= x"29_1A1A";

Cw42 <= x"2A_1616";

Cw43 <= x"2B_AAAAA";

Cw44 <= x"2C_C66";

Cw45 <= x"2D_0004";-

Cw46 <= x"2E_0000";

Cw47 <= x"2F_0000";

cw48 <= x"30_7FFF";