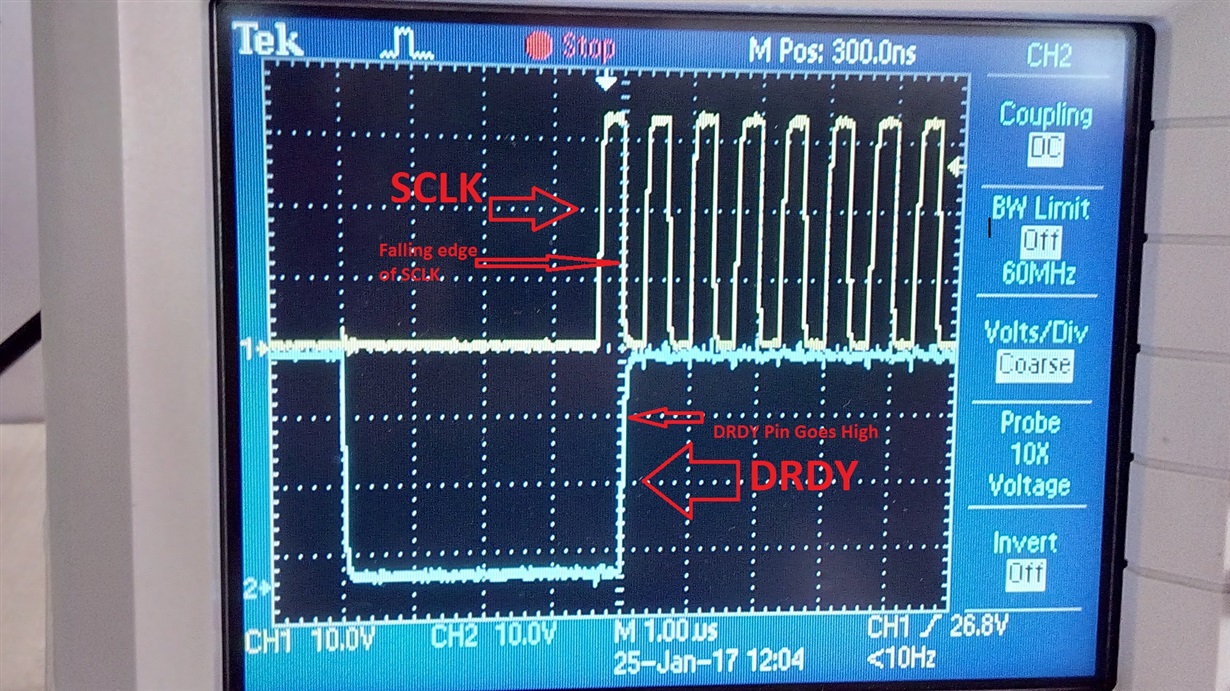

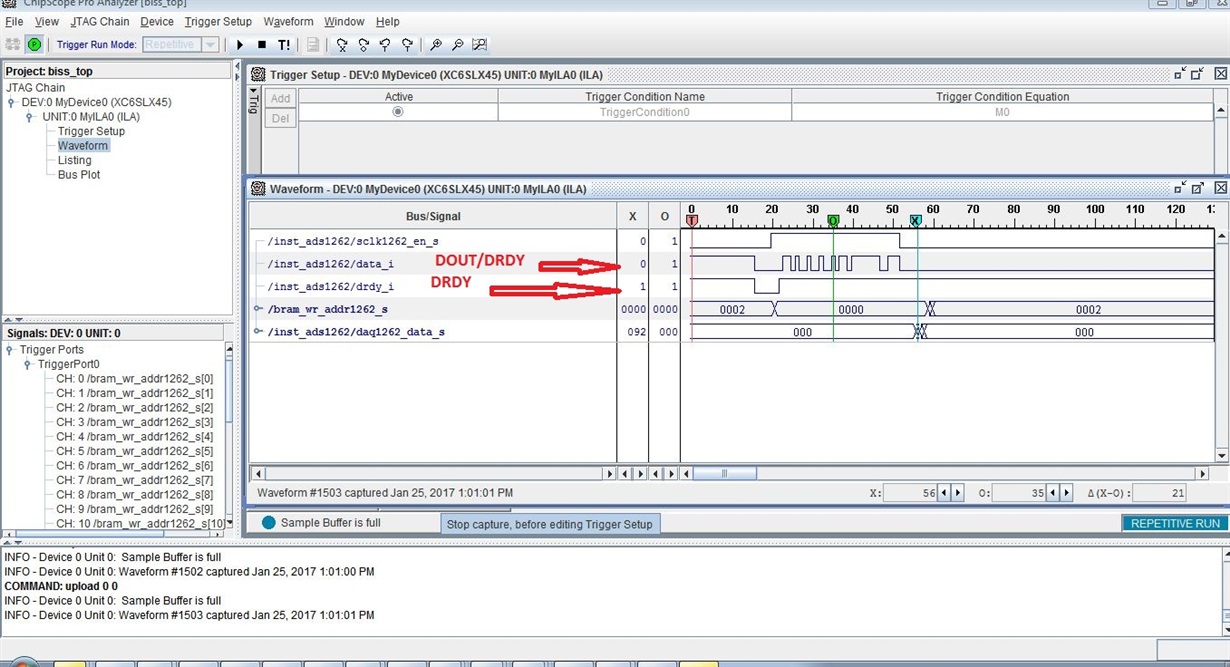

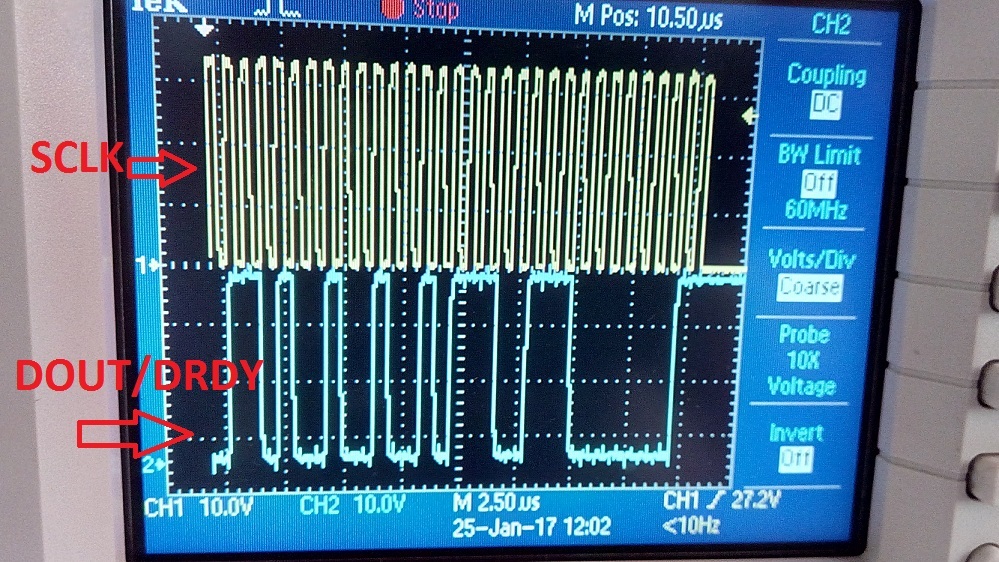

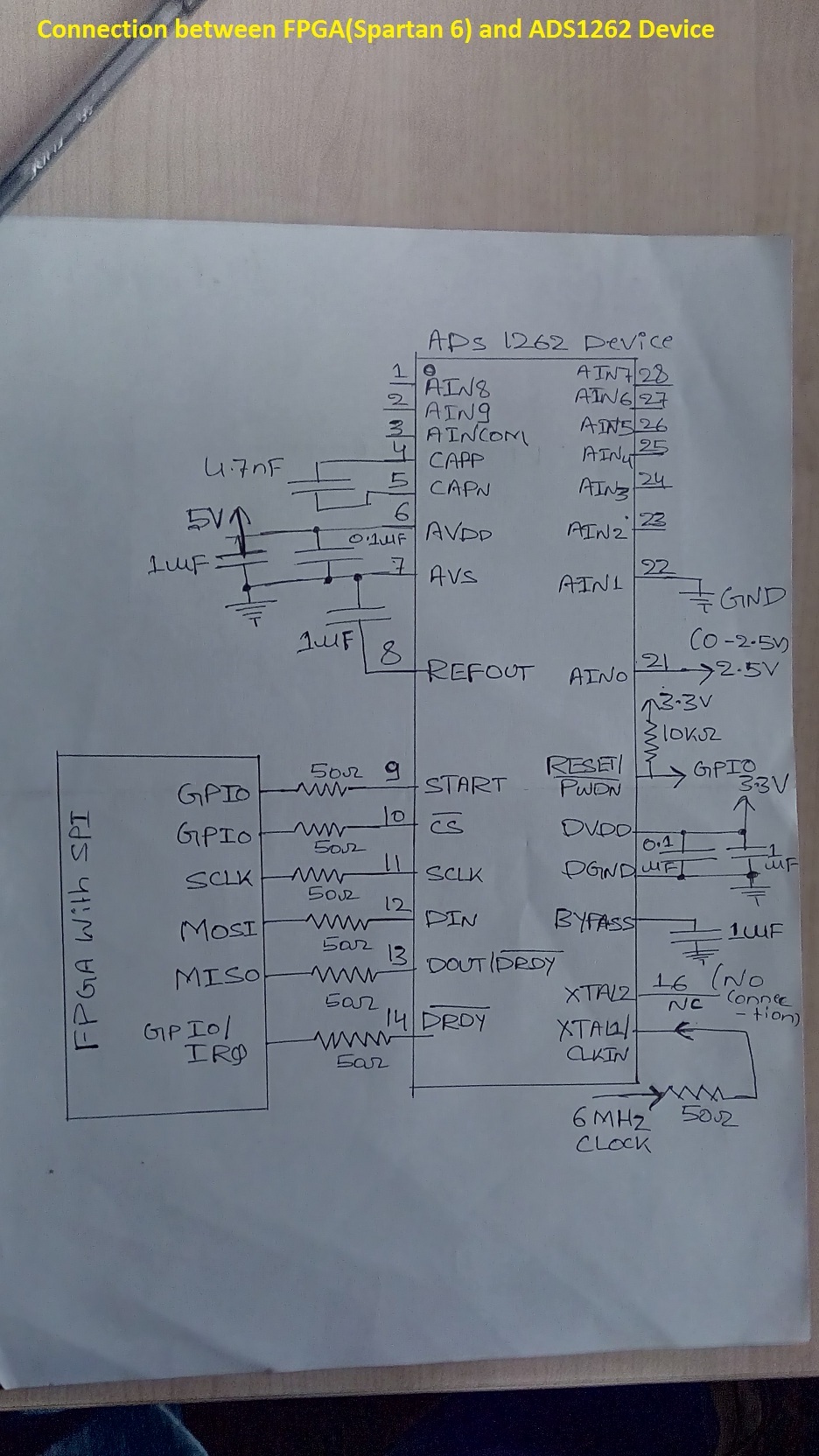

我一直在使用连接FPGA的ADS 1262。我在VHDL中编写了代码,通过检查引脚DOUT/DRDY可以看到数据对话,但无法捕获来自DOUT/DRDY引脚的串行数据。我已按照 数据表配置了所有模拟和数字电压。 我正在使用轮班登记方法更新数据(SIPO登记)。

下面将对我在VHDL中编写的代码进行编码

当start_adc_conv_st =>时

如果(start_i ='1'),则

启动<=高;

START_ADC_counter <= START_ADC_counter + 1;

如果(START_ADC_counter = 4),则

启动<=低;

ADC_1262 <= START_ADC_COV_ST1;

结束条件:

否则

启动<=低;

ADC_1262 <= START_ADC_COV_ST;

结束条件:

当start_adc_conv_st1 =>时

如果(START_ADC_counter =8),则

启动<=高;

start_adc_counter <= 0;

ADC_1262 <= drdy_detect1_st;

否则

START_ADC_counter <= START_ADC_counter + 1;

启动<=低;

ADC_1262 <= START_ADC_COV_ST1;

结束条件:

当drdy_detect1_st =>时

如果(drdy_i ='1'),则

ADC_1262 <= drdy_detect2_st;

否则

ADC_1262 <= drdy_detect1_st;

结束条件:

当drdy_detect2_st =>时

如果(drdy_i ='0')则

SCLK_enable_s <=高;

Bram_wr_cntr <= 06;

-- drdy_wait_cntr <= 0;

-- test_data <=(其他=>'0');

bram_wr_addr_s <=(其他=>'0');

ADC_1262 <= DATA_COLLECK_ST;

否则

ADC_1262 <= drdy_detect2_st;

结束条件:

当data_collect_st =>时

如果(CH1_cntr = low_cnt),则

SCLK_enable_s <=低;

bram_wr_en_s <=高;

ADC_1262 <= bram_write_data_st;

否则

如果(rd_EN1_I ='1'),则

received_data <= received_data(30 downto 0)和data_i;

CH1_cntr <= CH1_cntr - 1;

如果(CH1_cntr = 5),则

SCLK_enable_s <=低;

结束条件:

结束条件:

ADC_1262 <= DATA_COLLECK_ST;

结束条件:

当bram_write_data_st =>时

如果(bram_wr_cntr = low_cnt),则

Bram_wr_en_s <=低;

CH1_cntr <= 32;

CNTR <= 0;

received_data <=(其他=>'0');

ADC_1262 <= drdy_detect1_st;

否则

bram_wr_addr_s <= bram_wr_addr_s + 1;

Bram_wr_cntr <= bram_wr_cntr - 1;

ADC_1262 <= bram_write_data_st;

结束条件:

当其他人=>时

空;

结束案例;

结束条件:

结束流程;

提前感谢您