请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

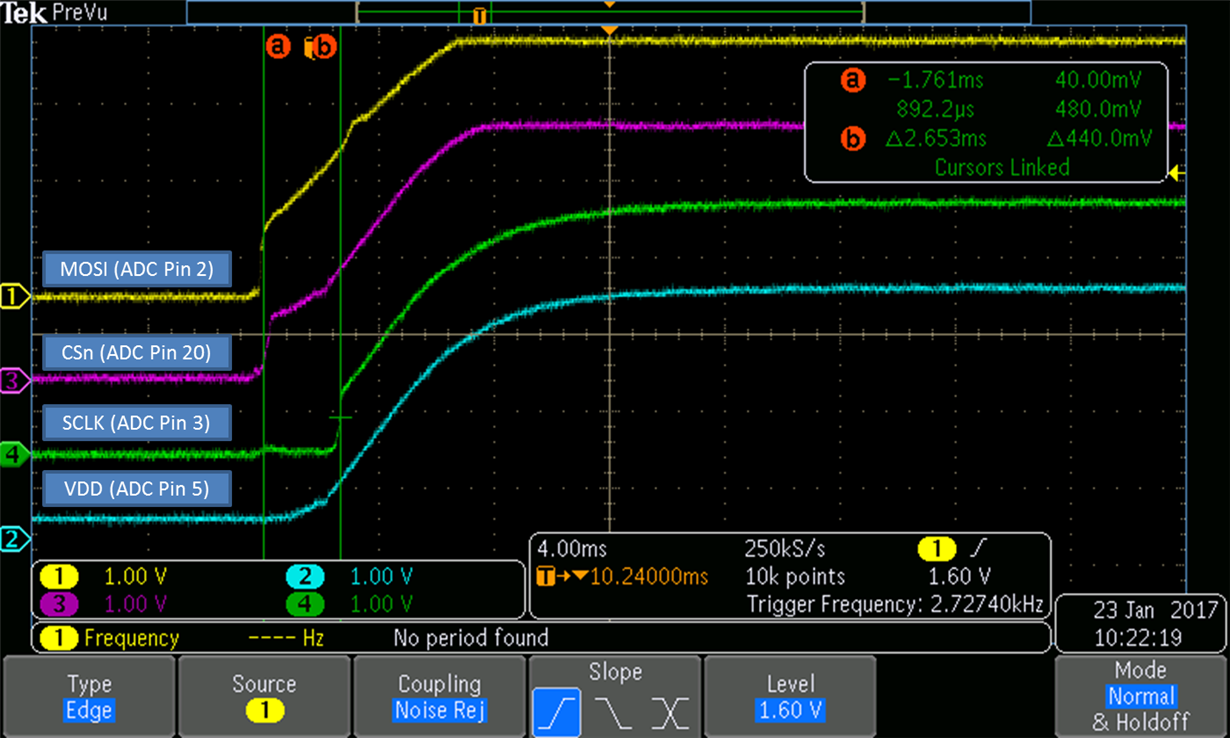

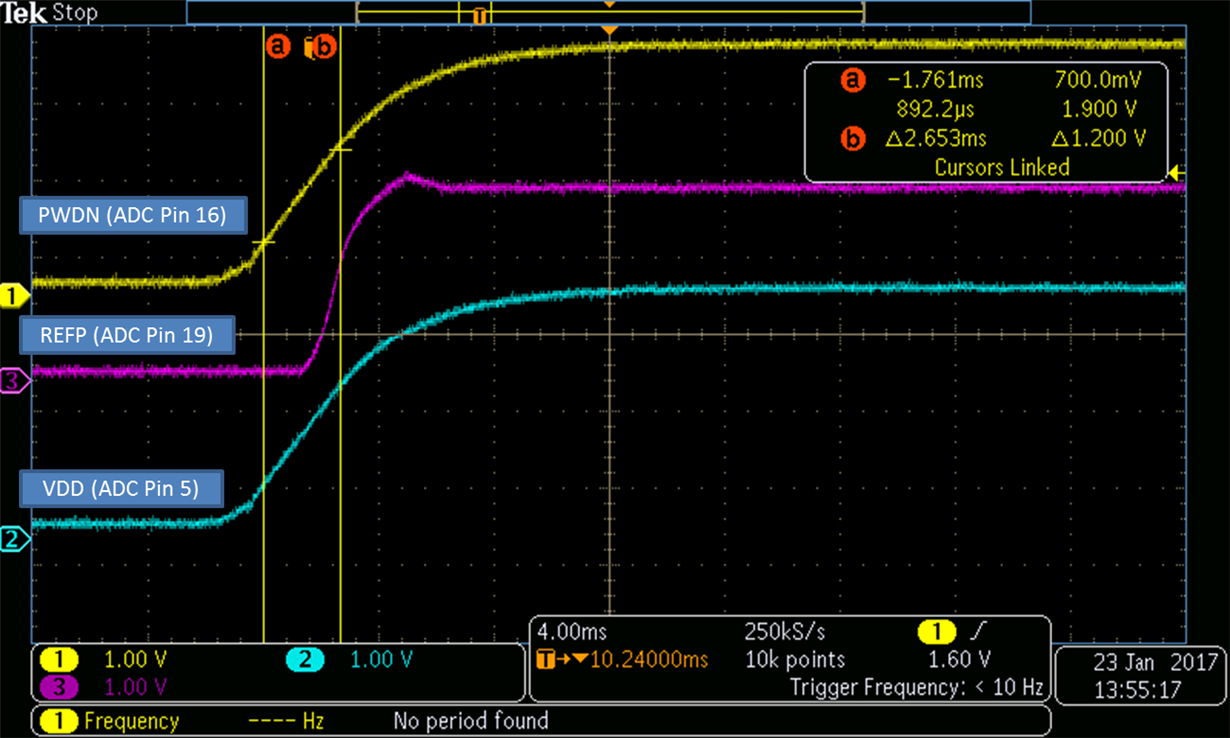

部件号:TLV2548 我们在产品中使用TLV2548IDW ADC (每台设备有多个器件)已有一段时间,并且遇到了一个非常罕见的事件,即在通电后,其中一个器件(每次都是相同的物理器件)不响应SPI事务, 或者通过所有的数据推动SPI miso (因为我们对miso有一个上拉,所以很难判断发生了哪些情况)。 同时,系统中的其他TLV2548设备运行良好。 所有 设备都将CFG寄存器初始化为相同的值(0x0004),这基本上是寄存器默认值,只有EOC/INTN输出引脚模式设置为EOC模式。 如果存在此问题,如果我们可以对处理器执行软重置,则相关ADC将开始工作,问题就会消失。 仅在开机时出现问题,并且在几个不同的装置上发生。 此外,当在这种失败状态(SDO所有一个输出或三态)下运行~10分钟时,我们的处理器在轮询EOC针以完成转换的例程中挂起。 这似乎表明设备突然脱离了坏状态并声称INTN (而不是EOC)。 是否有任何情况会导致设备在通电时进入这种不良状态?