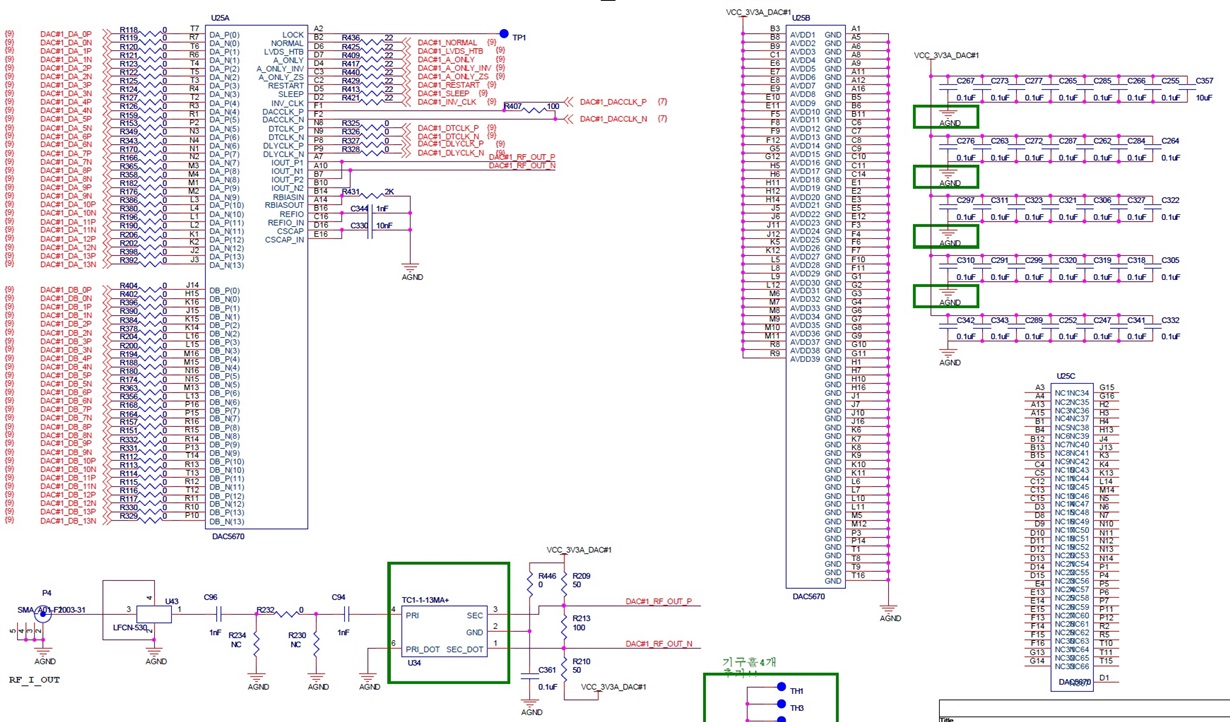

部件号:DAC5670

您好,

我在使用DAC5670器件时遇到问题。

输出信号的振幅与输入代码不匹配。

无论我向DAC输入什么代码,我都无法获得足够大的输出信号。

为了将此问题与任何其他可能的来源分开,我做了以下操作:

-我在FPGA中设计了2个寄存器,并将每个寄存器的输出连接到DA总线和DB总线。

-如果我写入value_A以注册A,写入value_B以注册B,那么DAC的输入代码应该是交替value_A和value_B (value_A,value_B,value_A,value_B,...)

通过执行此操作,我可以忽略DA,DB输入总线的设置/保持计时问题。

然后,我尝试按以下步骤编写寄存器:

1. value_A = 0x0,value_B = 0x0001

2.value_a = 0x0,value_B = 0x0002

3. value_a = 0x0,value_B = 0x0004

4. value_a = 0x0,value_B = 0x0008

5. value_a = 0x0,value_B = 0x0010

6. value_a = 0x0,value_B = 0x0020

7. value_a = 0x0,value_B = 0x0040

8. value_a = 0x0,value_B = 0x0080

9. value_a = 0x0,value_B = 0x0100

10. value_A = 0x0,value_B = 0x0200

11. value_a = 0x0,value_B = 0x0400

12. value_A = 0x0,value_B = 0x0800

13. value_a = 0x0,value_B = 0x1000

14. value_a = 0x0,value_B = 0x2000

15. value_a = 0x0,value_B = 0x3FFF

在我看来,输出信号应该随着上述测试的进行而加倍,但实际上不是。

输出信号变大,直到value_B=0x0100。 但从以下步骤中,事情变得越来越奇怪。

当value_B=0x0200时,输出信号与value_B=0x0020时的信号一样小。

当value_B=0x0400时,value_B=0x0040时,振幅相同。

当value_B=0x0800时,value_B=0x0080时,振幅相同。

当value_B=0x1000时,value_B=0x0100时,振幅相同。

我已多次重复检查原理图和FPGA约束的针脚分配。

每个板上有2个DAC,我们有4个板,因此我们手上有8个DAC,所有8个DAC都有相同的问题。

您是否有任何解决此问题的想法?