Other Parts Discussed in Thread: OPA320, REF3325, ADS7952, OPA625, OPA314, OPA192

主题中讨论的其他部件:REF3325,OPA320, OPA625,OPA314,OPA192

你好

简介:

我正在设计一个有11个光电二极管(PD)的主板。 PD连接到互阻抗放大器(TIA),TIA的输出被路由到ADS7952 (ADC)。 ADC 被配置为在手动模式下运行,1MHz作为SPI时钟。 读取每16.66毫秒预制一次,所有通道从0-11读取。 我已选择REF3325作为我的2.5V参考电压。 我已在缓冲模式下路由ADC ... MUX直接连接到AINP。

问题:

当我读取所有频道时,我可以看到CH8噪音很大,并且有偏移。 即使我对所有通道应用恒定电压,我也可以注意到CH8显示的值要低得多。 我无法解释为什么。 在数据表中,我没有找到任何可以解释CH8这种行为的信息。

其他信息:

因为TIA,我正在使用OPA314。 我尝试更改OPA320和OPA625。 OPA625的性能最佳,但CH8上仍有相当大的噪声和偏移。 我尝试使用LTC6268。 此时噪音和偏移消失了。 但LTC6268的功耗为16mA,11PD的功耗接近200mA。 超出了我的电力预算?

问题:

CH8是否有任何特别之处显示了此类行为?

如果我要在MUX和AINP之间使用具有缓冲区的ADC,问题是否会消失?

对于缓冲实施,我是否仍需要在每个通道上使用150p的上限?

我的主板有3.3V电源。 这意味着我不能将OPA192用作V缓冲区。 您是否可以推荐在3.3V下工作并可与ADS7952配合使用的V缓冲器?

示波器图片:

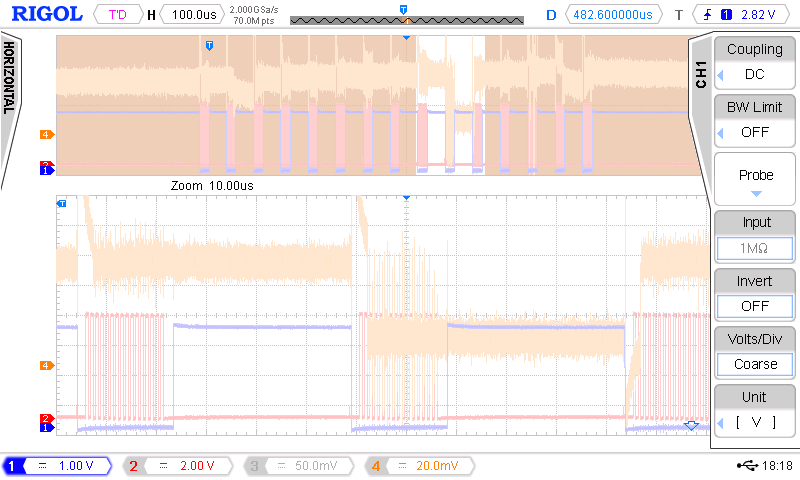

我用我的范围对板做了一些测量。 我将我的采集与SSN (紫色线)同步。 红色线表示SCK,黄色线表示MUX和AINP之间的信号。

正如您在黄线上看到的那样,在第10 SSN低电平上,噪音要高得多。 有趣的是,当ADC在读数中显示偏移时,不会出现预期的压降。

下一幅图片显示了噪音信道上的缩放

正如您所看到的那样,SCK的每个过渡上都有黄线(MUX和AINP之间的信号)峰值(红线)。 当我将其与采集进行比较时,我还没有看到测量信号的闪烁或闪烁(黄线)。 请参见下一张图片。

这是之前仅一个通道的缩放采集。 如您所见,没有噪音。

我还通过我的示波器获得了SPI信号。 下图:

我放大了3次采集。 我想演示一下我们是如何解决ADS7952的。 正如您从MOSI所看到的,信道计数正在从一个测量值进展到另一个测量值。 此外,miso还显示ADS7952正在为我们提供进展结果(miso增量的前4位正确)。 在最后一个测量中,我会看到故障MUX到AINP信号。

非常感谢你的帮助

示意图:

我的主板的顶级文件

变速器阻抗放大器

ADS7952