主题中讨论的其他部件: ADS52J90, LMK0.4826万

您好,支持团队,

我们的客户现在正在使用ADS52J90EVM评估JESD204B通信。

客户更改SYSREF_SERDES信号的频率。

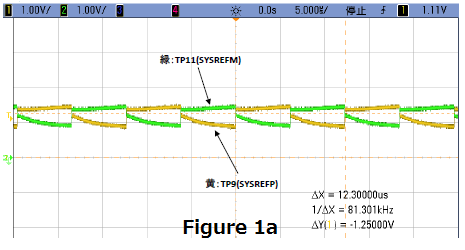

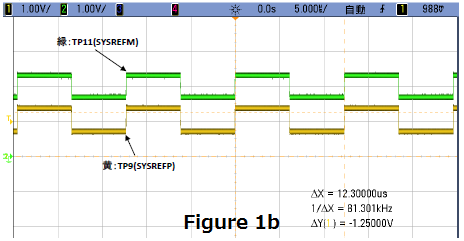

当SYSREF_SERDES信号输入到ADS52J90的频率降低时,LVDS信号的波形将变暗,如图1a所示,或者它们将处于图1b所示的相位。

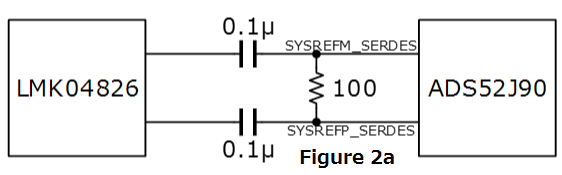

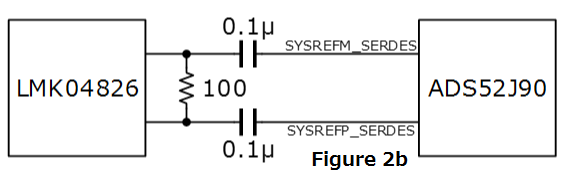

当端接电阻从交流耦合电容器后面(图2a)更改为前面(图2b)时,LVDS信号的波形将正常。

这是一个问题。

1.如图2a所示,当终端电阻器放在交流耦合电容器后面时,为什么波形变暗或同相?

2.如图2b所示,将终端电阻器放在交流耦合电容器之前是否有任何问题?

请教我。

此致,

Tachibana先生