您好,

我正在测试ADS5404在500MSPS的自定义PCB上的操作。 我正在使用4MHz的测试CW信号来驱动单个数据转换器通道。

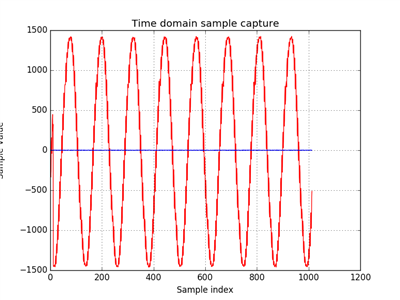

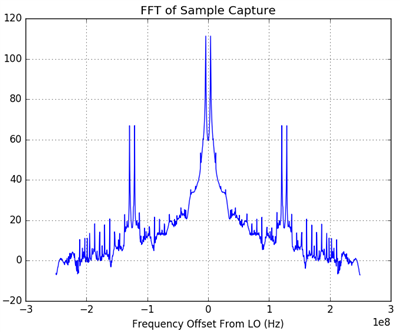

我已启用DC校正,以消除数据表第23页中提到的DC和FS/2处的毛刺。 我还启用了自动校正功能,我知道这应该会将FS/2 - Fin spur降低到大约80dbc,但在我的情况下,它始终保持在~42dbc。 我已附加了ADC数据的时间和频率域图。

我还运行了禁用自动校正的测试。 生成的图解无法区分。

我已在操作过程中读回ADC寄存器的值,如下所示。 是否有任何已知的使用条件或实现细节会导致自动更正不起作用?

地址:0x0值:0x8000

地址:0x1值:0x8202

地址:0x2值:0x780

地址:0x3值:0xb18

地址:0xe值:0x0

地址:0xF值:0x0

地址:0x1a值:0xb18

地址:0x2b值:0x4b

地址:0x2C值:0x0

地址:0x37值:0x0

地址:0x38值:0xxffdf

地址:0x3a值:0x481b

地址:0x66值:0xFF

地址:0x67值:0xFF