大家好,

我正在使用ADS5294 EVM作为我的ADC,使用Zynq (ZC-7020)作为FPGA进行14位高速串行LVDS ADC数据(DDR)捕获。 让我向你们解释一下我的要求和问题。

我开发了硬件和软件部件,能够通过ADC发送和接收简单的位模式,并在FPGA上接收。 主要是移动版本,即如果我发送了11111110000000,我将收到00111111100000或此版本的任何其他版本。 但当我发送信号时,无论是移位信号还是正确信号,我都无法正确接收。 就像如果我发送斜面(在ADC板内部生成),接收信号的整体形状就像斜面,但有些位会丢失或跳过。

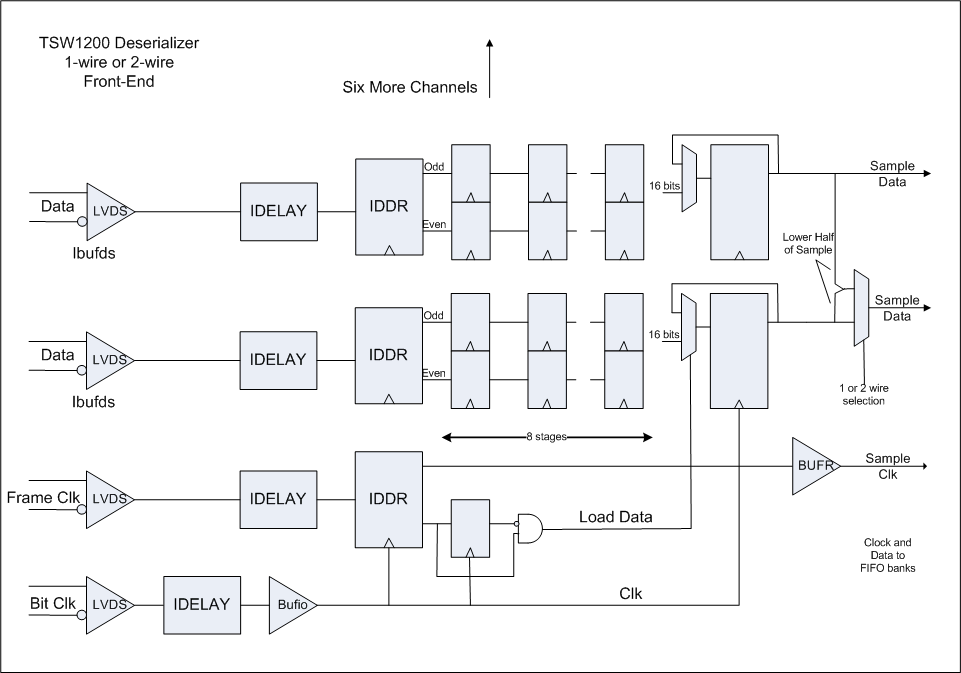

我遵循的方案是设计用于捕获的硬件。

我正在按照本指南进行设计:

我已经制作了精确的数字3-1。然后我将DDR输出组合成14位的样本。

现在我面临的问题是:

- 本指南第10页图3-1显示在IDEAY之后应使用BUFIO将位时钟转发给IDDR。但当我使用BUFIO时,在路由过程中收到错误。 错误:"[DRC 23-20]规则违规(RTSTAT-1)未路由网络- 1个网络未路由。 有问题的总线和/或网络为DESIGIND_1_I/iddr2_IP_0/inst/cBufferedIO。" 是否有必要在此处使用BUFIO?

- 以及没有正确接收斜坡的问题是什么。

此致