请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

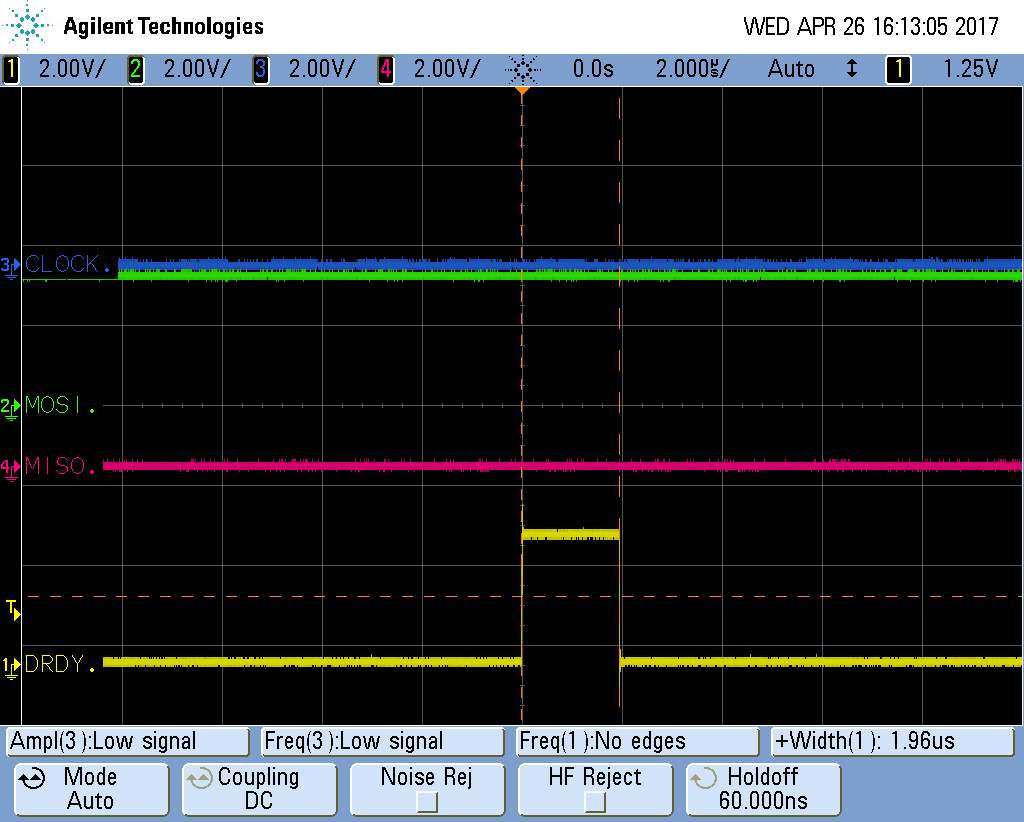

部件号:ADS1194 我已将芯片编程为RDATAC模式,但DRDY信号不是数据表的标准高信号,当数据就绪时,它在1.96us时会变低。 我的DRDY正常低,在采样频率下为1.96us时会变为高。 这是数据表问题还是我的设置无法正常工作?

我还在图58中发现了一些错误。 第一个WREG CONFIIG3应为0xC0而不是0x80。 其次,WREG CONFIIG2 shuld为0x30而不是0x10。