大家好,

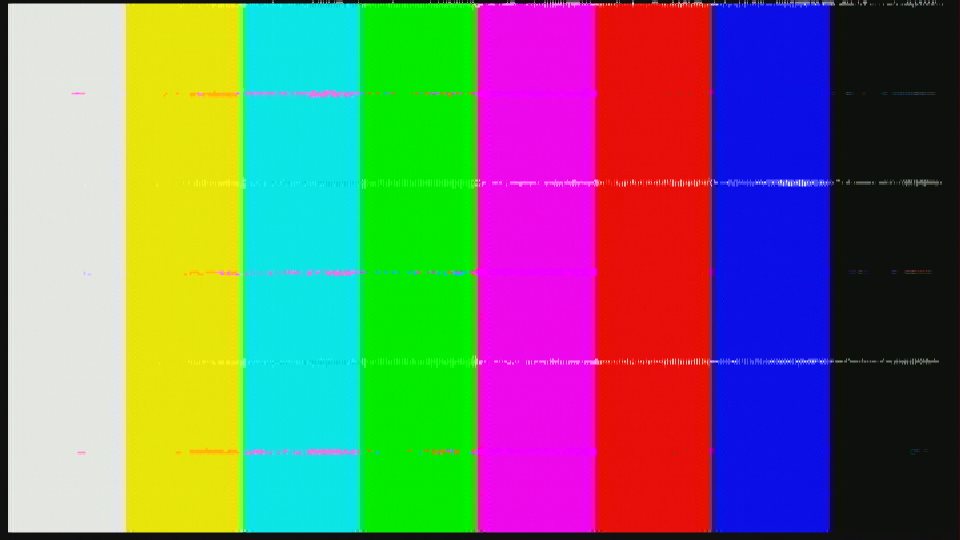

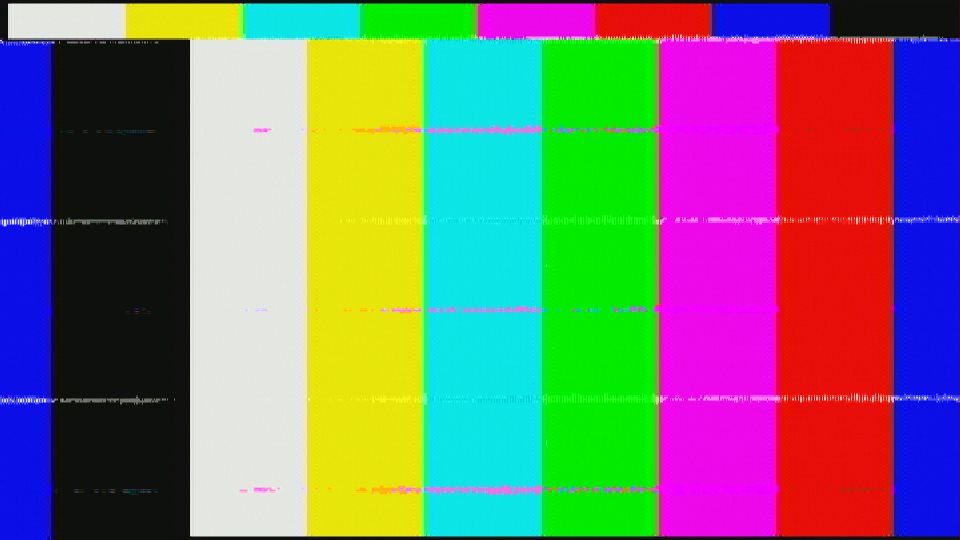

我们的定制CCA设计中存在TVP5158的问题。 当温度降至-30摄氏度以下时,我们开始在视频上看到线条伪影。 我附上了几个示例。

我们已验证是否遵循了重置顺序,并且正在应用2.3 2补丁,以防万一。 通过验证针脚处的输入信号是否正常,问题已缩小至解码器。 如果应用了蓝色的同步测试模式,则输出看起来正常。 只有当它开始处理输入视频时,我们才会看到伪影(包括来自发生器的蓝色测试图案)。

除非我们重置芯片或重启主板,否则问题不会消失。 即使我们恢复温度,视频仍显示损坏。 我们还在多个主板上看到过这种情况,因此我们非常确定这不是一次性部件或PWB问题。

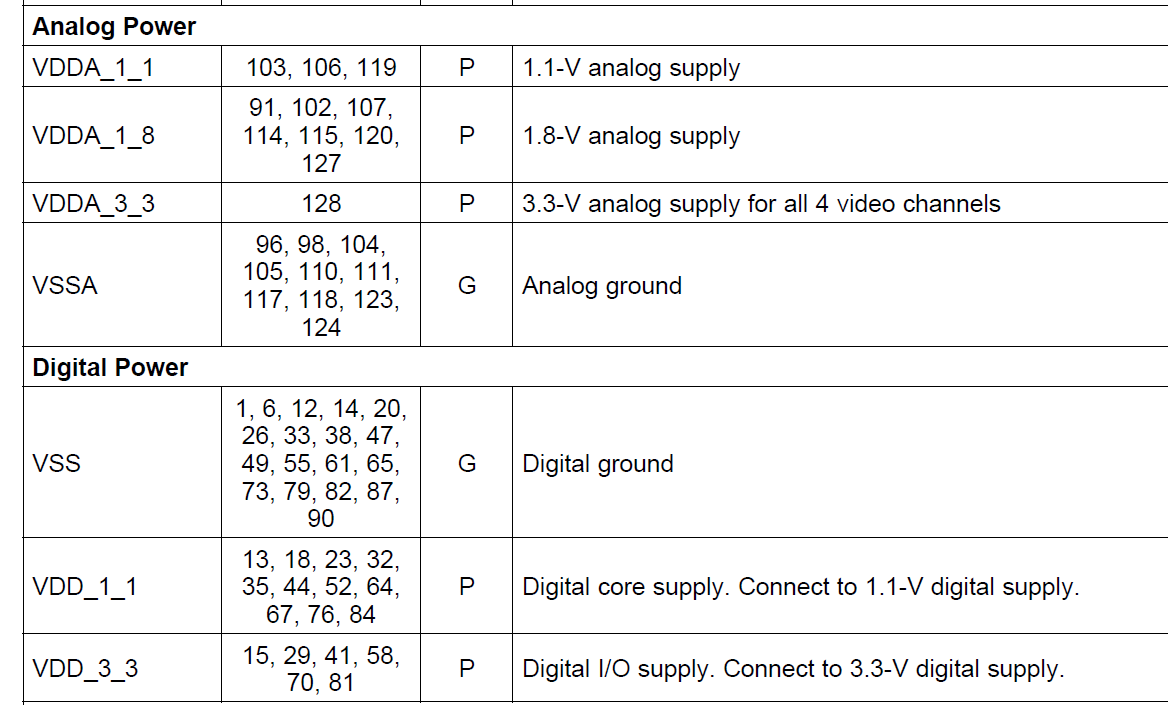

除修补程序外,我们还修改了以下寄存器,以便根据我们的用例配置该部件。

名称,注册,值

TVP5158_decoder WREN,0xFE,0x0F

TVP5158_AVD_OUT,CTRL_1,0xB0,0x60

TVP5158_AVD_OUT,CTRL_2,0xB1,0x17

TVP5158_POWER_CTRL,0x1A,0xF0

TVP5158_output_form_CTRL_1,0xA8,0x04

TVP5158_output_form_CTRL_2,0xA9,0x44

TVP5158_BLUE_SC_Y_CTRL,0x90,0x29

TVP5158_BLUE_SC_CB_CTRL,0x91,0xF0

TVP5158_BLUE_SC_CR_CTRL,0x92,0x6E

TVP5158_OFM_MODE_CTRL,0xB2,0x25

TVP5158_Brightness_contrast范围,0x12,0x13

我希望只需简单的注册调整即可解决此问题!

提前感谢您的帮助!

Jason