您好!

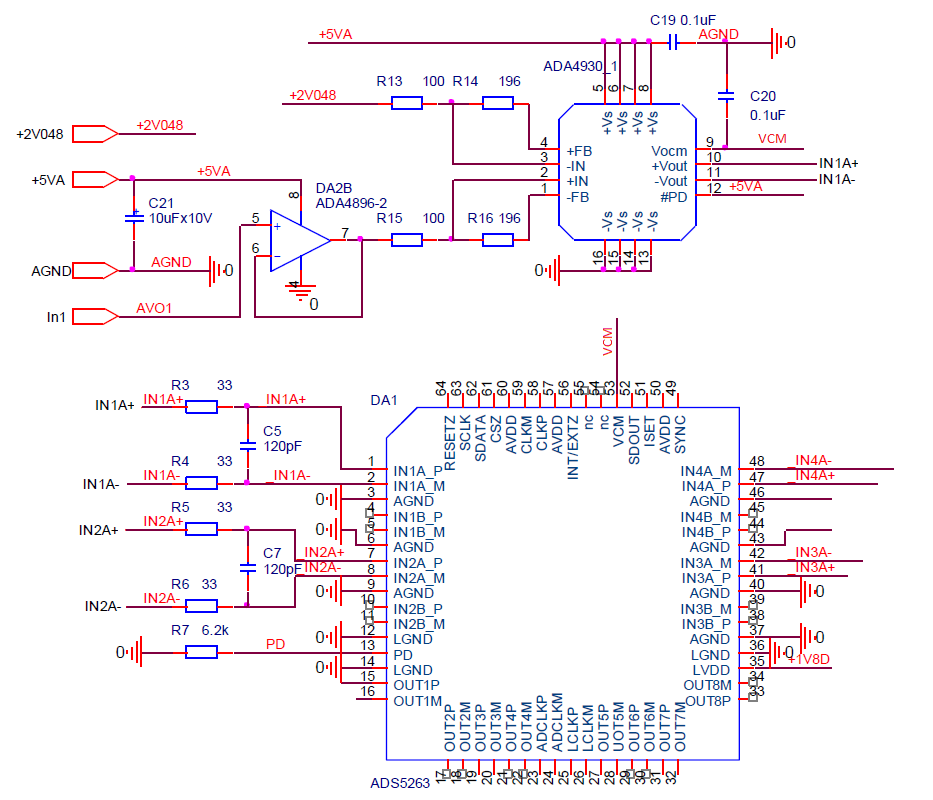

我们使用ADA4930驱动ADS5263。 ADC输入端信号的最大转换速率为47V/us。 采集时间应为~85ns。 下面是电路的一个碎片:

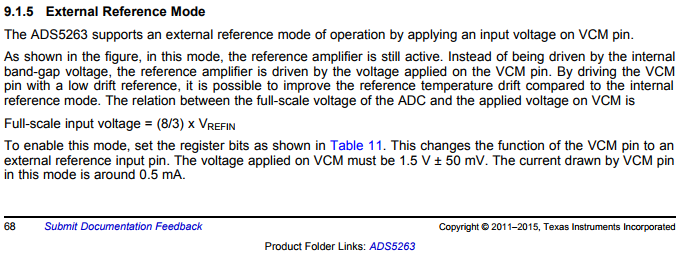

我们的设计是否有任何错误? 我对ADS5263的数据表(第63页)中的短语感到困惑:“建议使用与每个输入引脚串联的5 Ω 至15 Ω 电阻器来抑制由封装寄生物引起的振铃。 还需要为共模切换电流提供低阻抗(50Ω Ω)。 这可通过使用两个电阻器实现,每个输入端接至共模电压(VCM)。'

1)为什么我们要将这些5 Ω 至15 Ω 电阻器与每个输入串联? 我认为我们需要在"储液罐"电容器C5/C7和ADC的采样电路之间有一些可能的阻抗。

2)您能否解释为什么我需要"每个输入端接到共模电压的两个电阻器"?

另一个问题是模拟输入等效电路(第62页的图90)。 我想模拟由采样电路引起的故障。

3)这三个开关的正时图是什么? 在转换期间,采样开关处于"关闭"状态,其余时间处于"打开"状态。 对吧? 第三个开关(最右侧)的正时图是什么?

谢谢!