在“线程: LMK0.4828万”中讨论的其它部件

我正在将ADS54J54 与LMK0428时钟抖动消除器结合使用,并观察ADC的奇怪行为。 LMK0428为ADC提供500 MHz时钟以及SYSREF输入。 我正在使用SYSREF的脉冲/单次激发方法,这是数据表推荐的方法。

下面是我的步骤和结果:

我使用数据表中的以下步骤对ADS54J54进行编程:

7.3 ................................................................12 JESD204B接口初始化顺序

通电后,内部JESD204B数字块必须按以下步骤顺序进行初始化:

1.将JESD RESET AB/CD和JESD INIT AB/CD设置为0 (地址0x0D,值0x0000)

2.将JESD init AB/CD设置为1 (0x0D,0x0202)

3.将JESD重置AB/CD设置为1 (0x0D,0x0303)

4.配置所有其它JESD寄存器和时钟设置。 如果这些设置稍后更改,则会进行初始化

必须重复顺序。

5.将JESD重置AB/CD设置为0 (0x0D,0x0202)

6.将JESD重置AB/CD设置为1 (0x0D,0x0303)

7.等待两个SYSREF脉冲

8.将JESD init AB/CD设置为0 (0x0D,0x0101)

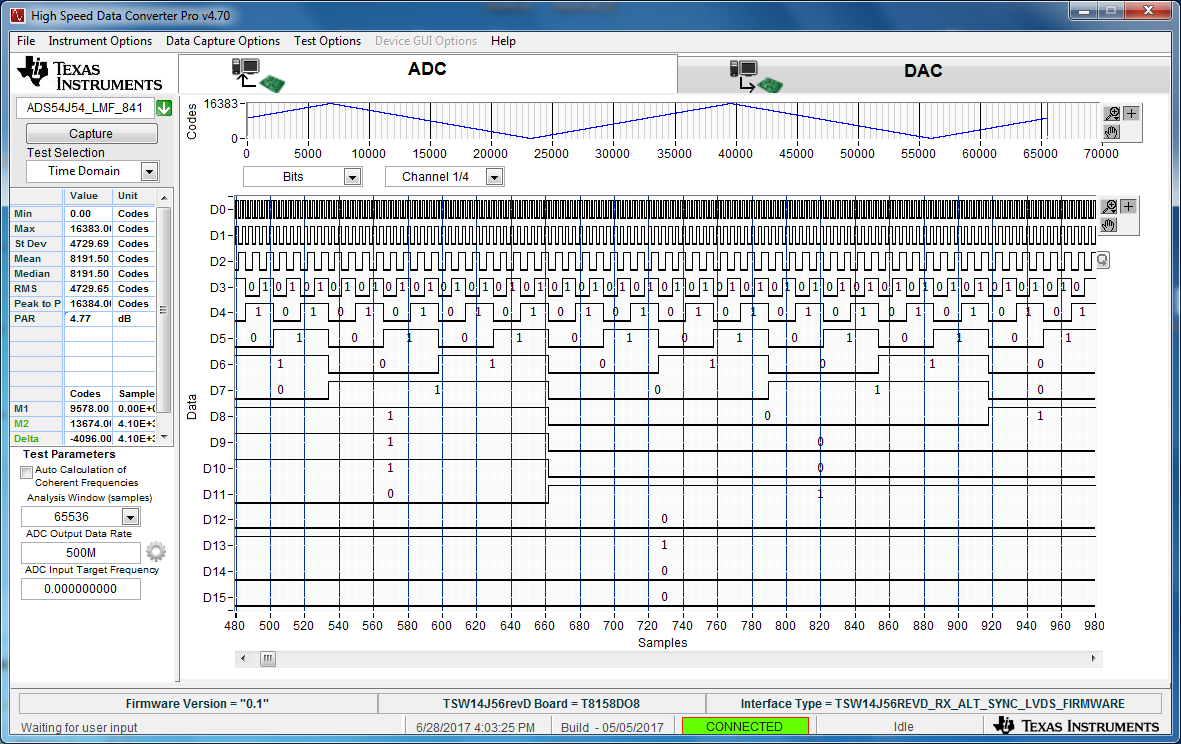

执行步骤8后,设备将立即开始发送K字符。 这是不可预料的。 根据数据表,在确认SYSREF并进行同步之前,我不应接收K字符。 请参见下图。 如果我断言SYSREF,那么k字符将短暂停止,其他字符将被传输,但它们与ILA过程不一致。 接收到几十个随机字符后,接收到的数据将无限期地恢复为k字符。

奇怪的是,SYNC似乎对ADC行为没有任何影响。

提前感谢您的帮助。