请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

部件号:DAC38J84EVM 主题中讨论的其他部件:DAC38J84

您好,

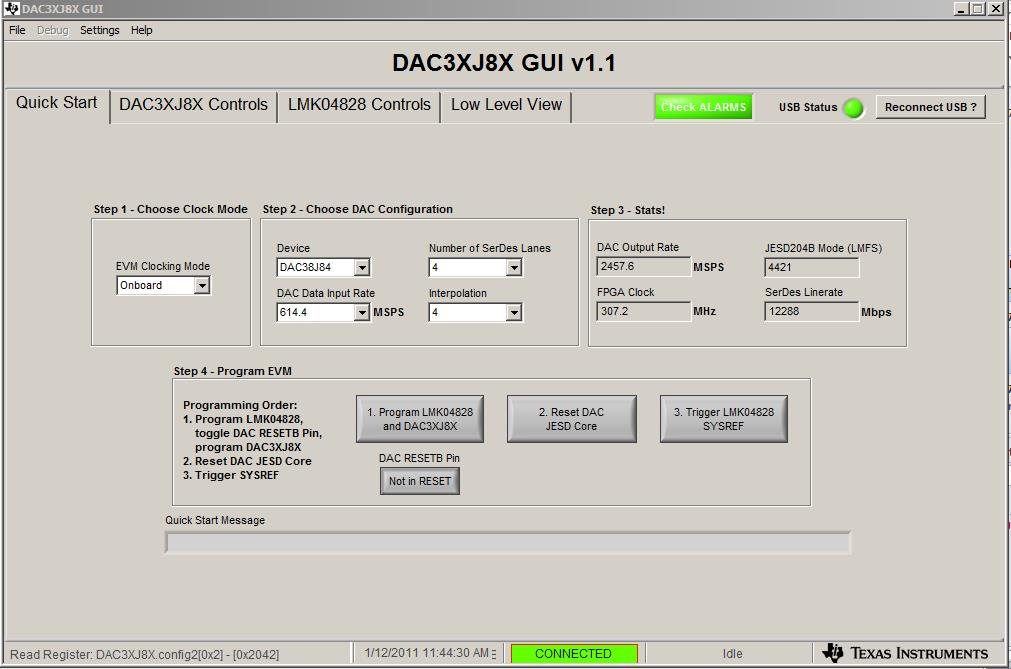

我正在使用DAC38J84 EVM,并注意到FPGA时钟是DAC输入数据速率的1/2,我想知道这两个数字来自何处? 在我的应用程序中,我正在4421模式下运行设备,示例时钟= 2457.6Msps,这给出了1.2288万Mbps的信道速率。 使用bi-4插值,我知道输入速率必须为614.4MSPS,以使通道速率分子学正确计算,但我只是想知道如何在FPGA中处理x2。 FPGA架构运行频率为307MHz,但在串行化之前,数据速率却翻倍了吗?

谢谢!

下面是我的设置的屏幕截图: