主题中讨论的其他部件: LMX2531

您好,

我们想了解有关TI ADC P/N ADC08D1020的一些信息。

我们正在将IGLOO2 FPGA P/N M2GL150-1FC1152与ADC08D1020连接起来,并且已观察到可能的不兼容性。

特别是ADC所需的LVDS时钟信号将由FPGA提供,频率设置为240MHz。

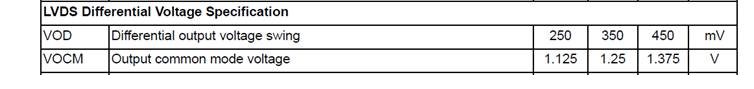

FPGA以LVDS标准生成时钟信号,在下一张图片中,VOD参数将显示出来,如相关数据表中所报告。

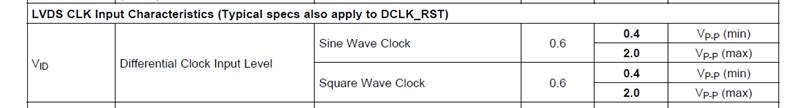

ADC具有以下LVDS CLK输入特性,如相关数据表中所报告。

请注意,FPGA最低输出LVDS电平(VOD)为250mV,而ADC可将400mV管理为最低输入LVDS信号(VID)。

我们原本期望VOD (最低)> VID (最低)。

因此,即使ADC LVDS CLK输入在相关的数据表中被定义为LVDS标准(与FPGA使用的标准相同),这两个器件似乎也不兼容。

您是否认为这可能是真正的不兼容? 也许我们对数据表的理解可能不正确。

如果答案是"是",您能否建议解决此问题的方法?

此致

Antonio L.