线程中讨论的其他部件: ADS1294, ADS1298, THS4551, THS4521, TINA-TI

您好,

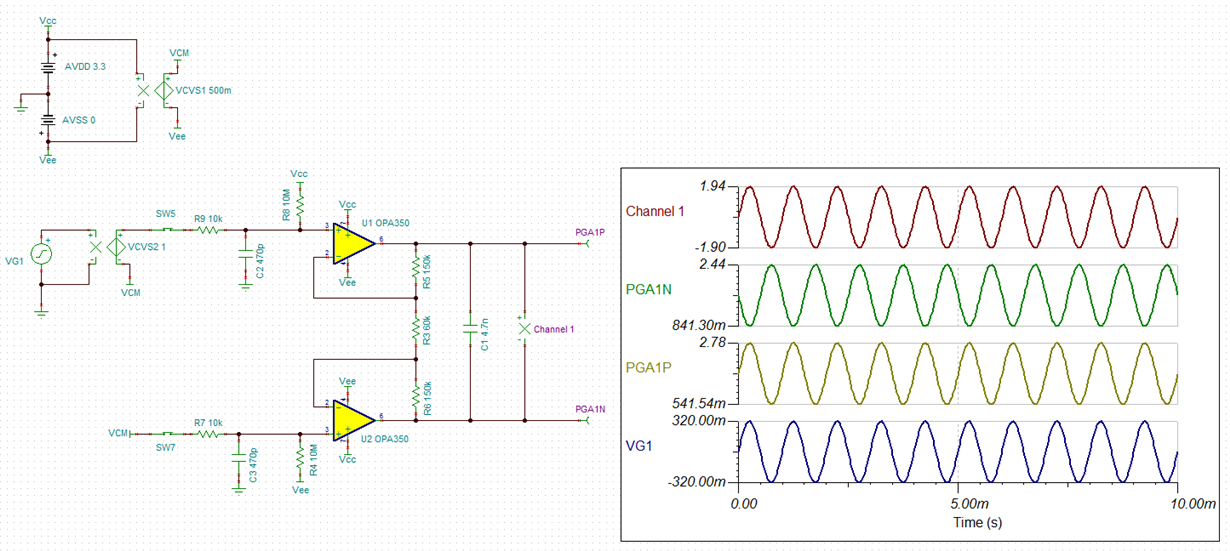

我正在使用ADS1292进行EMG信号采集。 在将信号馈入ADS1292之前,我的电路具有过滤和放大阶段,因此输入信号将是单端的。 根据数据表,建议使用差分输入,我了解这样做的好处,但由于它不适合我的应用,我需要采取另一种方式。 意味着我使用分压器将负极输入Inn驱动至中端电源。 我只是想知道我的设计是否正确。 我需要承认,我是这一领域的新手,在这个论坛上找不到合适的问题答案。

1)单端输入电路是否像我一样正确? 是否有比使用分压器更好的方法来提供中间电源?

2)它是否与我提供的单电压电源一起工作? (AVDD = 3.3V,AVSS = 0V)

3)根据数据表,RLDIN/RLDREF也可用作单端输入。 这是更好的方式吗? 但我仍然喜欢使用右腿驱动...

感谢您的支持