主题中讨论的其他部件: DAC8830

我认为这个转换器的文档有一个问题,就是CPAH=1或CPAH=0对于SPI模式。 如果我们继续使用可靠的维基百科,我们会发现以下信息:

- 在CPOL=0时钟的基本值为零,即空闲状态为0,活动状态为1。

- 对于CPHA=0,数据在时钟上升沿(低→高转换)捕获,数据在下降沿(高→低转换)更改。

- 对于CPHA=1,数据在时钟的下降沿(高→低转换)捕获,数据在上升沿(低→高转换)更改。

- 在CPOL=1时,时钟的基本值为1 (CPOL=0的反转),即空闲状态为1,活动状态为0。

- 对于CPHA=0,数据在时钟的下降沿(高→低转换)捕获,数据在上升沿(低→高转换)更改。

- 对于CPHA=1,数据在时钟上升沿(低→高转换)捕获,数据在下降沿(高→低转换)更改。

和:

| SPI模式 | 时钟极性 (CPOL/CCKP) | 时钟相位 (CPHA) | 时钟边缘 (CKE/NCPHA) |

|---|---|---|---|

| 0 | 0 | 0 | 1. |

| 1. | 0 | 1. | 0 |

| 二 | 1. | 0 | 1. |

| 3. | 1. | 1. | 0 |

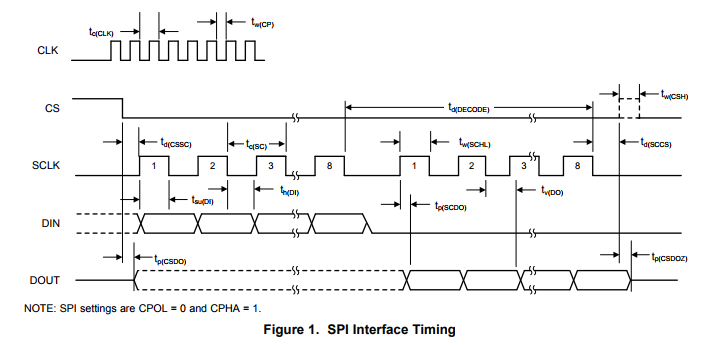

查看ADS127L01的数据表时,我们会看到以下内容:

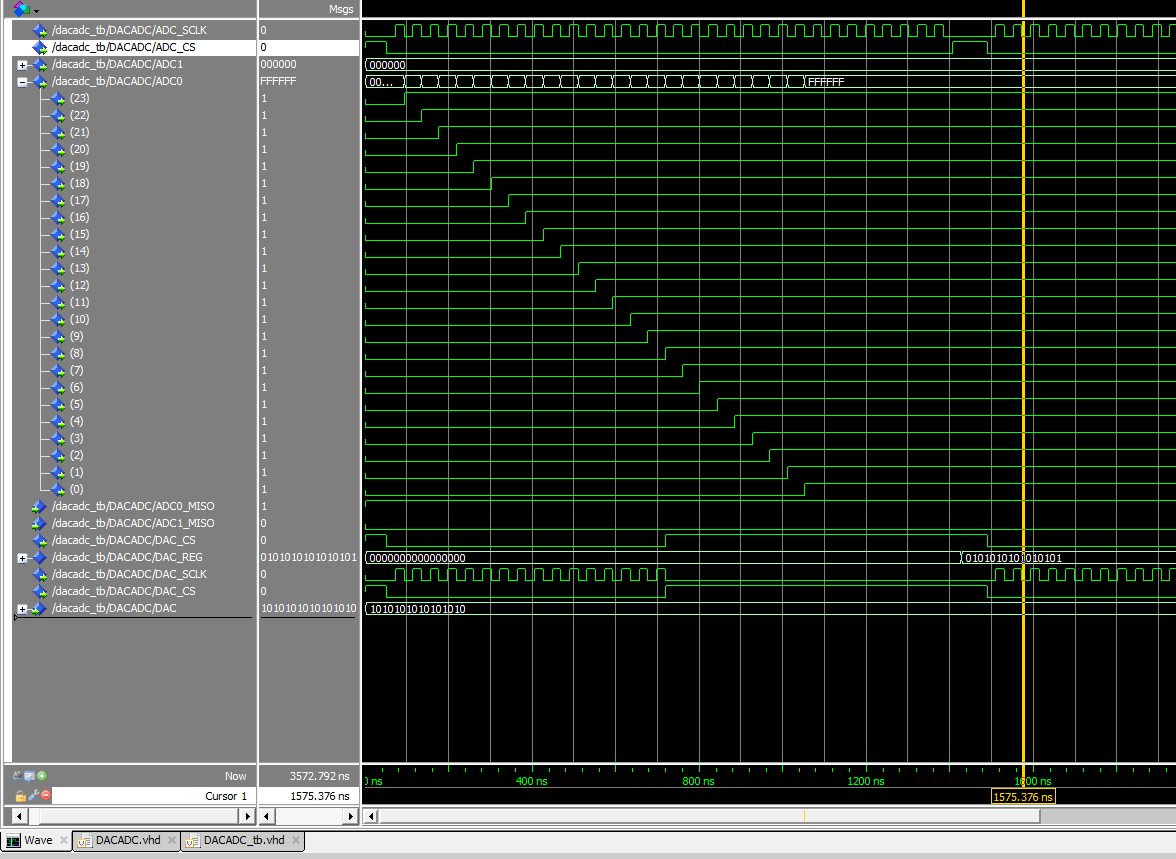

尽管说明CPHA = 1,但计时图与CPHA = 0一致,因为数据在上升沿上发生变化,并锁定在下降沿上(第12页)。 此外,文本中还显示"仅支持SPI模式1 (CPOL = 0,CPHA = 1)"。 我以前曾将此ADC与TI MCU一起使用过(TivaC):

SSIConfigSetExpClk (SSI0_BASE,SysClockSet(),SSI_FRF_MOTO_MOTO_MODE_1,SSI_MODE_MASTER,2000万, 16);

所以我猜错误是时间图? 或者我有些困惑吗? 我的开发系统仍然使用MCU,但由于该系统(引线)中的相移较大,我可能需要做大量的调整才能获得可靠的结果。

詹姆斯。