我们已将 ADC31JB68连接到Xilinx Artix-7 FPGA,并使用千兆位收发器GTP IP进行接口。

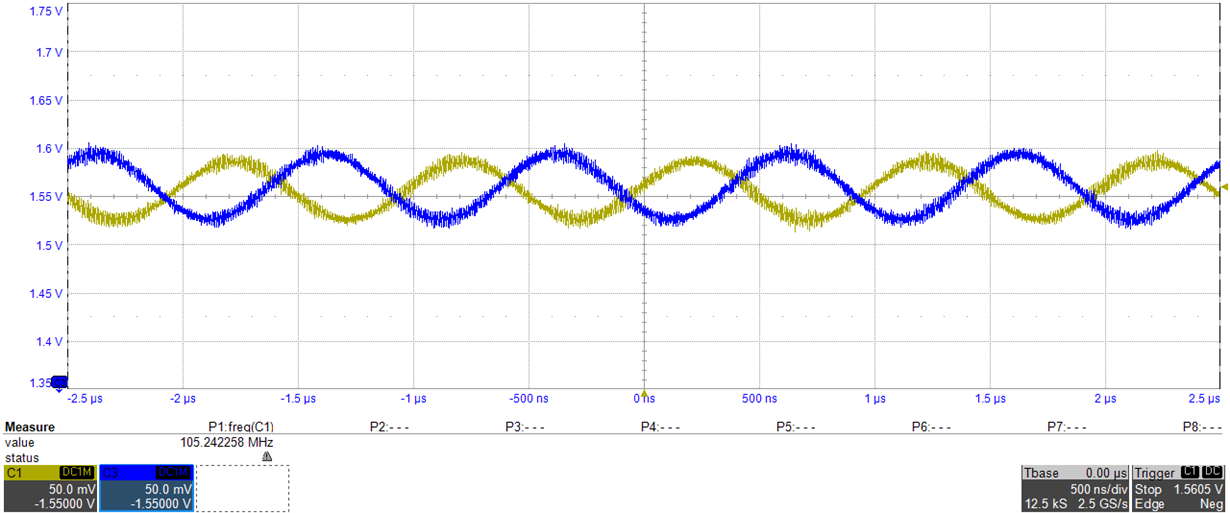

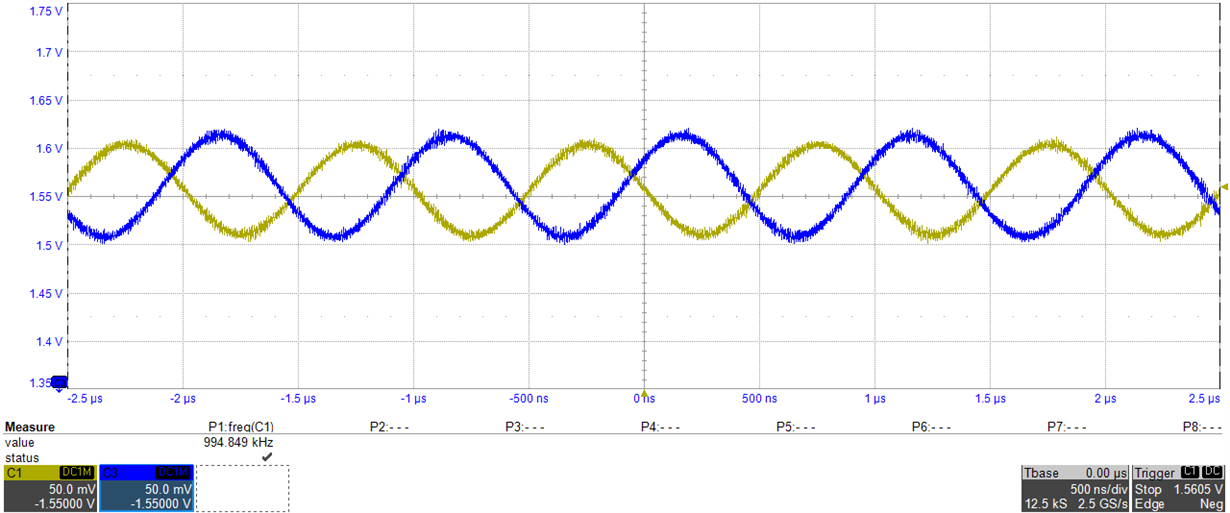

问题在于开机后同步被驱动为低电平。 两个通道上均应显示K 28.5 数据(Xilinx IP的并行数据输出中显示xBC)。 有时两个通道都会发送此数据,当同步驱动得较高时,可以看到正确的捕获数据。 从这里开始,接口将始终正常工作。 但是,在其他情况下,没有一个或只有一个车道传输K 28.5 ,并且复位或重新同步的组合似乎都不会改变这种情况。 重新加载FPGA图像将更改输出正确K 28.5 数据的通道。

似乎存在某种开机或数据对齐问题。