请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

部件号:DAC5672A 大家好,

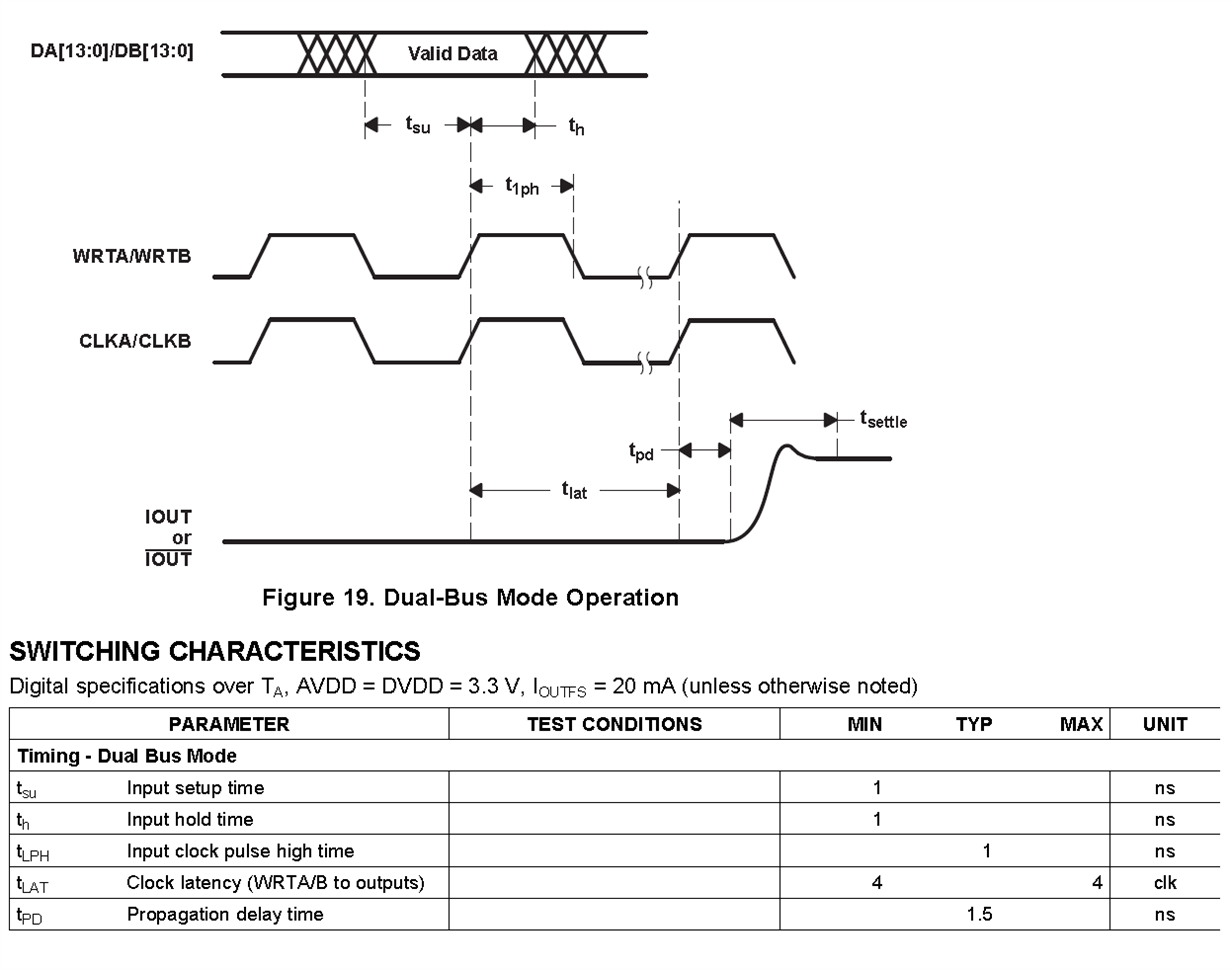

客户希望进一步了解DAC5672A 数字计时

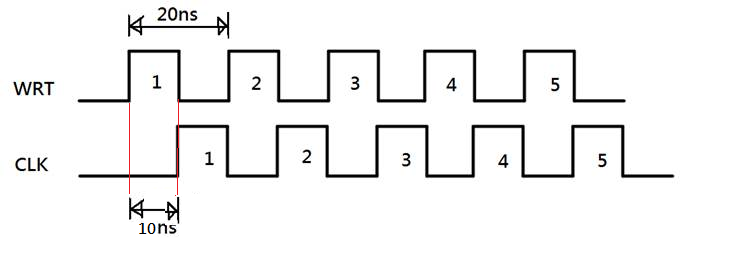

如果客户正在执行双总线模式,并且他们没有在硬件中缩短WRTA/B和CLK,则他们计划通过FPGA通过软件进行修复。 他们目前所做的是先提高WRTA/B脉冲,然后再提高CLK。 他们会尽量将它们分开至少2纳秒。

问题:

(1) Tsu和Th规范,指WRTA/WRTB。 (非短WRT和CLK)

(2)数据表中说,将WRT和CLK最小分开2ns。我们没有最大规格?

(3)低于数字定时是否完全有效?

谢谢。

此致,

Andrew