主题中讨论的其他部件:LMK0.4828万,

您好!

我的主板具有FPGA Kintex UltraScale,LMK0.4828万和ADC12J4000,在3 GHz旁路模式下运行(6Gbps线路速率)。 LMK为ADC提供3 GHz时钟,为Kintex GTH提供单个150 MHz时钟,为ADC和FPGA提供Sysref信号。 FPGA内部的JESD内核通过GTH计时。此配置已使用EVM+KCU105进行检查,工作正常。

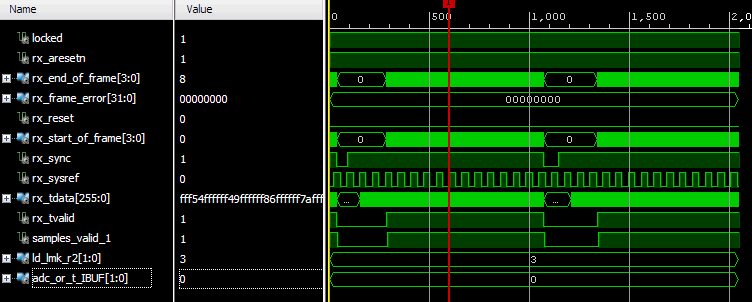

我的董事会成功通过了ILA阶段。 接收到一定数量的数据(大约20-30个多帧和输入正弦信号在那里是完美的),然后FPGA将同步降至低。 JESD内核在Rx_frame_error[]信号处未指示任何错误。 PRBS23 IBER测试也通过了,没有任何错误,并且眼睛开阔。

我尝试以同样的结果关注:

- 更改多帧中的帧数;

- 使用单Sysref和永久Sysref时钟

- 更改ADC中的Sysref相位

- 启用和禁用加扰器

它看起来像框架末尾的错误控制符号,但我不知道如何修复它

还有其他想法吗? 谢谢你。