大家好,

我们在菊花链配置中有四个ADS127L01:

- SCLK,MOSI,NCS:通用于所有芯片

- 开始:通用于所有芯片

- DRDY:或一起连接至微处理器

- DAISYIN:接地在最后一个芯片上,连接到其它芯片上前一个芯片的DOUT

- dout:连接至以下芯片上的DAISYIN (以及第一个芯片上的微处理器的miso)

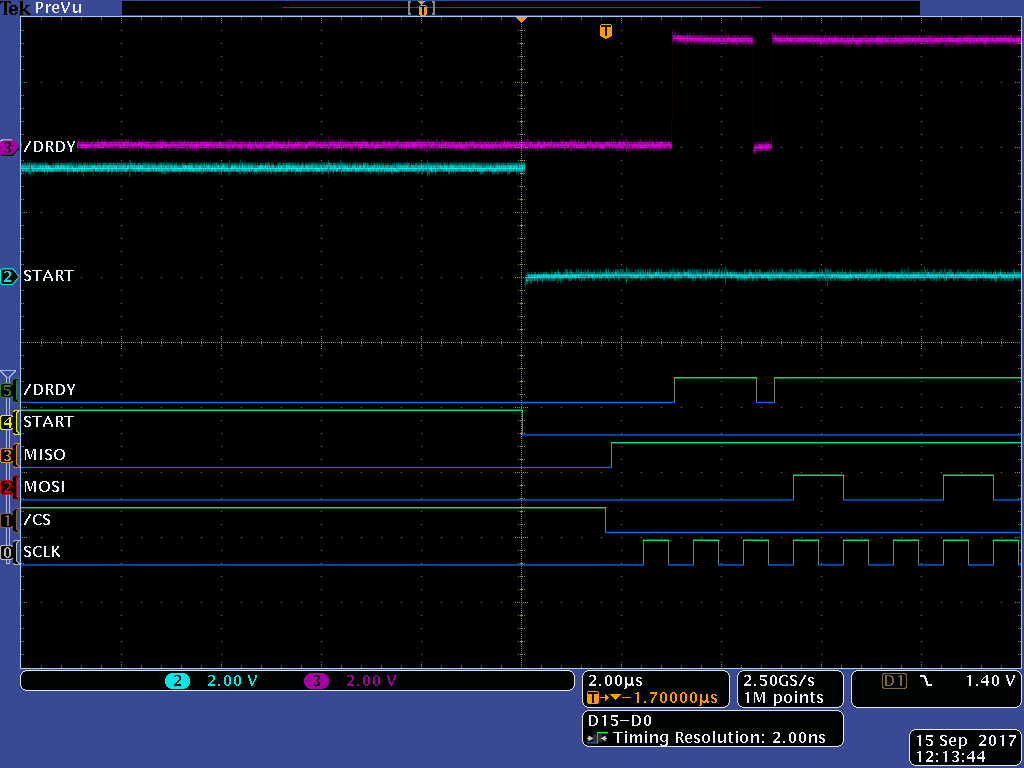

芯片的配置是LP,OSR 128,Wideband 1过滤器,使用SPI模式读取结果。 下图概述了MCU-ADC接口的行为:

前两个读数成功(所有CRC都正确),但在最后一个读数上,数据损坏(SW停止进一步读取)。 下图显示了读数#1…的详细视图

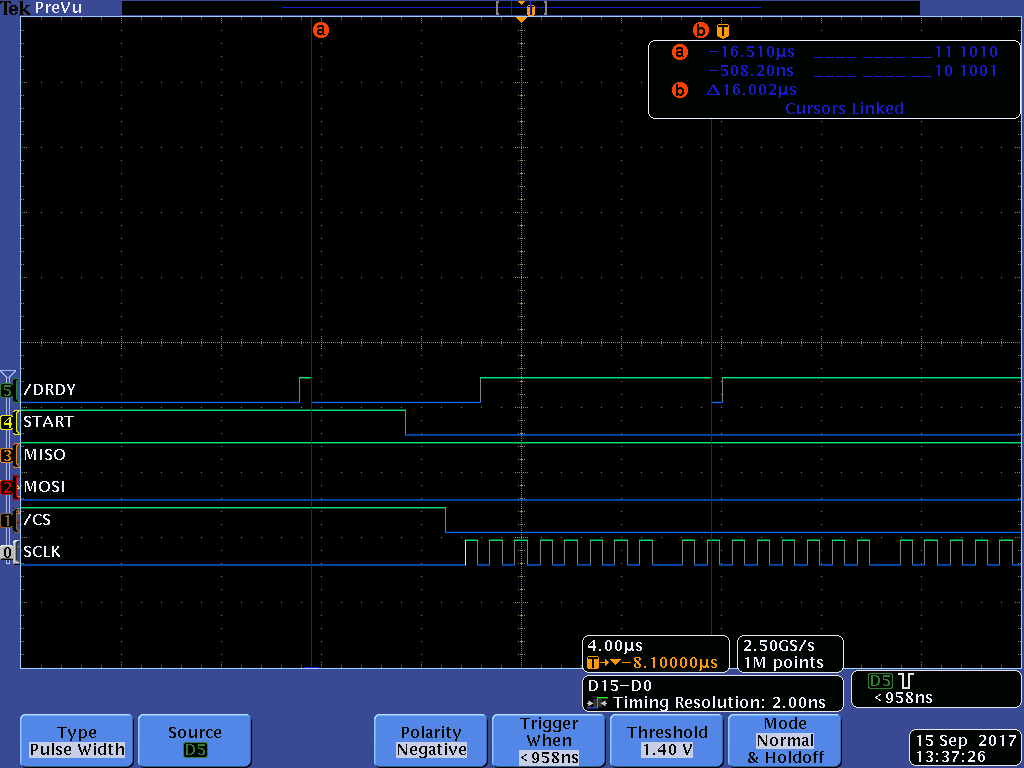

…最后一个图显示了读数#3的详细视图:

我能发现的唯一区别就是

- 在正确的读数下,CS激活后DRDY脉冲不存在,或者在第一个数据位移出之前存在

- 如果读数错误,则在移出第一个数据位后会出现DRDY脉冲。

问题:

1.我们是否正确处理DRDY信号(OR-ING)?

2. DRDY脉冲的目的是什么?

3. CS激活后,当启动低时,DRDY负脉冲是什么意思?

感谢您的意见

一月