主题中讨论的其他部件: ADC12J4000, ADC12DJ3200, LMX2581, LMK0.4828万

您好!

我已获得adc12j4000EVM rev,并尝试将其连接到我的vcu108 Xilinx板。 旁路模式3760 MSPS。

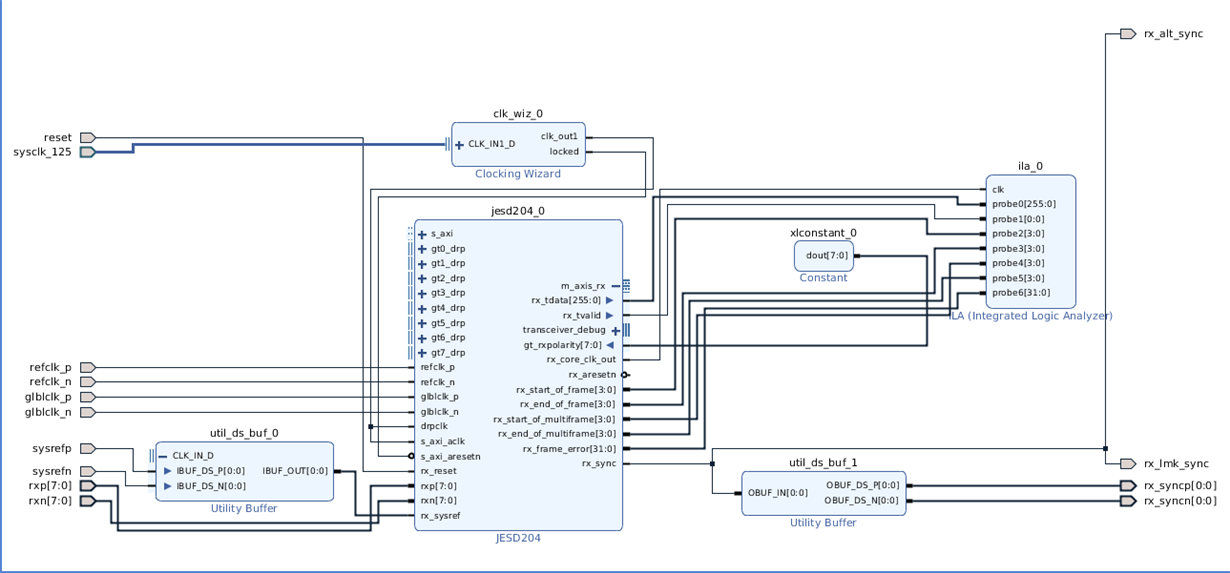

根据此ADC的数据表,我正在使用JESD(Xilinx JESD 204b IP core v GUI)的以下参数-来自ADC 7.1 的默认参数:

F=8

K=4

L=8

LineRate = 7.52Gbps

参考时钟=188MHz

正缘上的SYSREF

使用全局时钟1

抢着

sysref始终打开

重新同步时需要sysref

在其他收发器 控制端口中,我更改了gt_rx端口的极性;在ADC GUI v 1.1 中,我在旁路模式下按“程序时钟”按钮;对于测试,我打开了短/长传输测试。

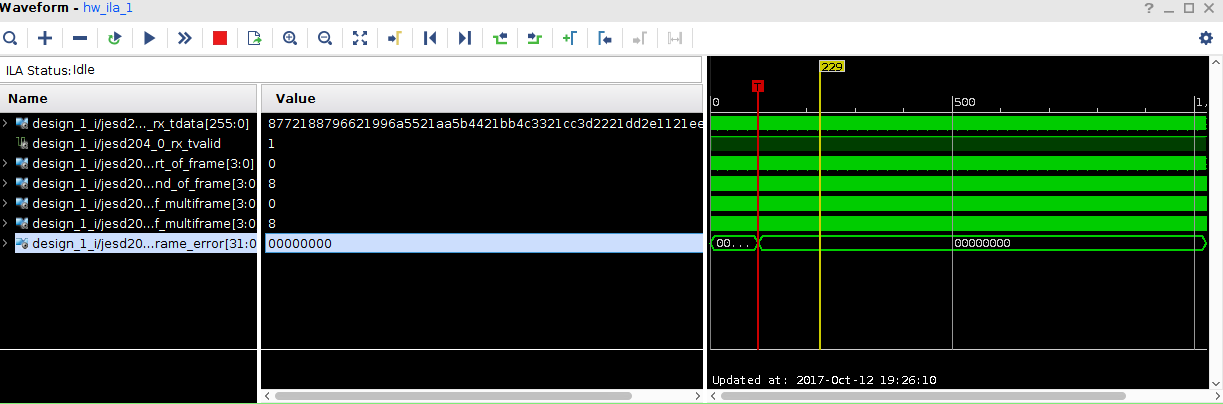

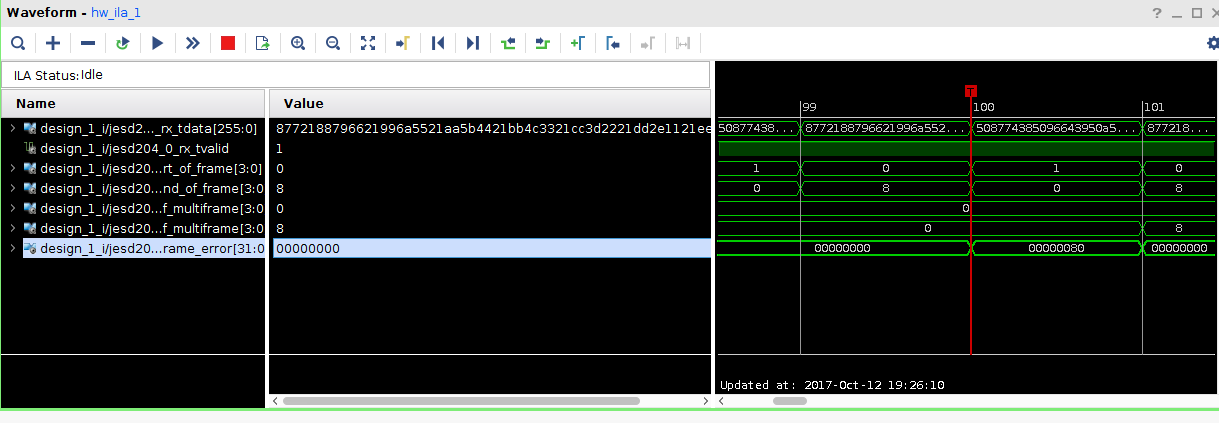

所以我希望在输出总线上看到rx_frame_error总线全部为零和序列。

(块设计和芯片范围打印在附件中)