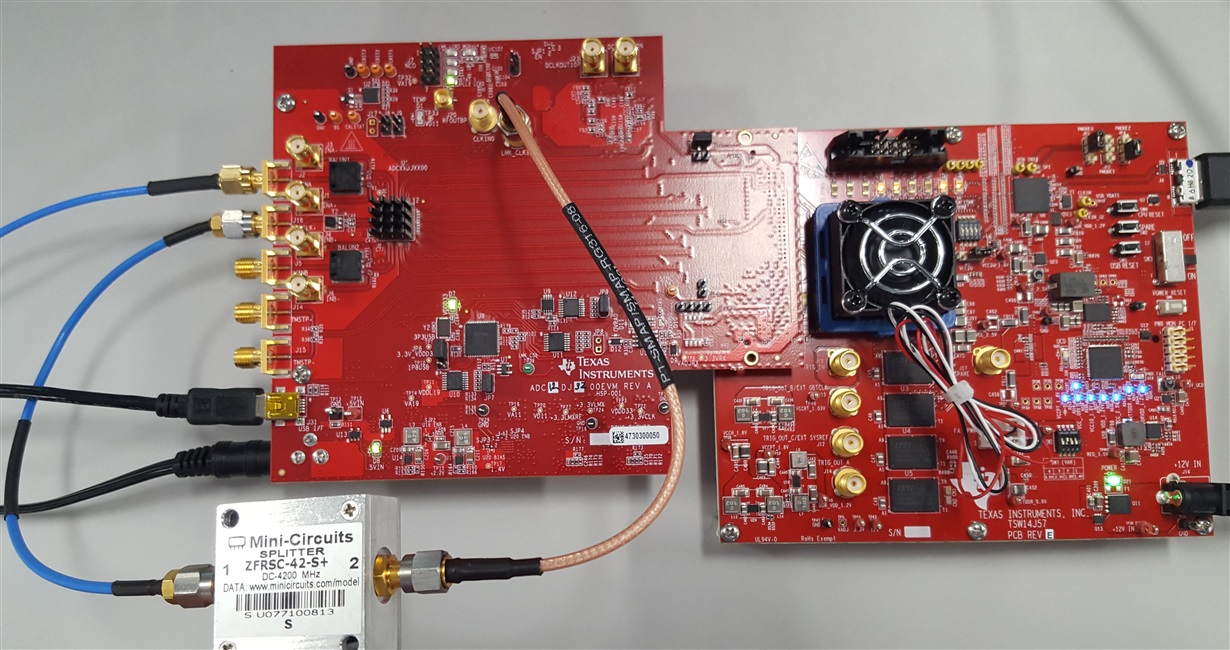

线程中讨论的其他部件:ADC12DJ3200, TSW14J57EVM, TSW14J56EVM,

您好,TI团队:

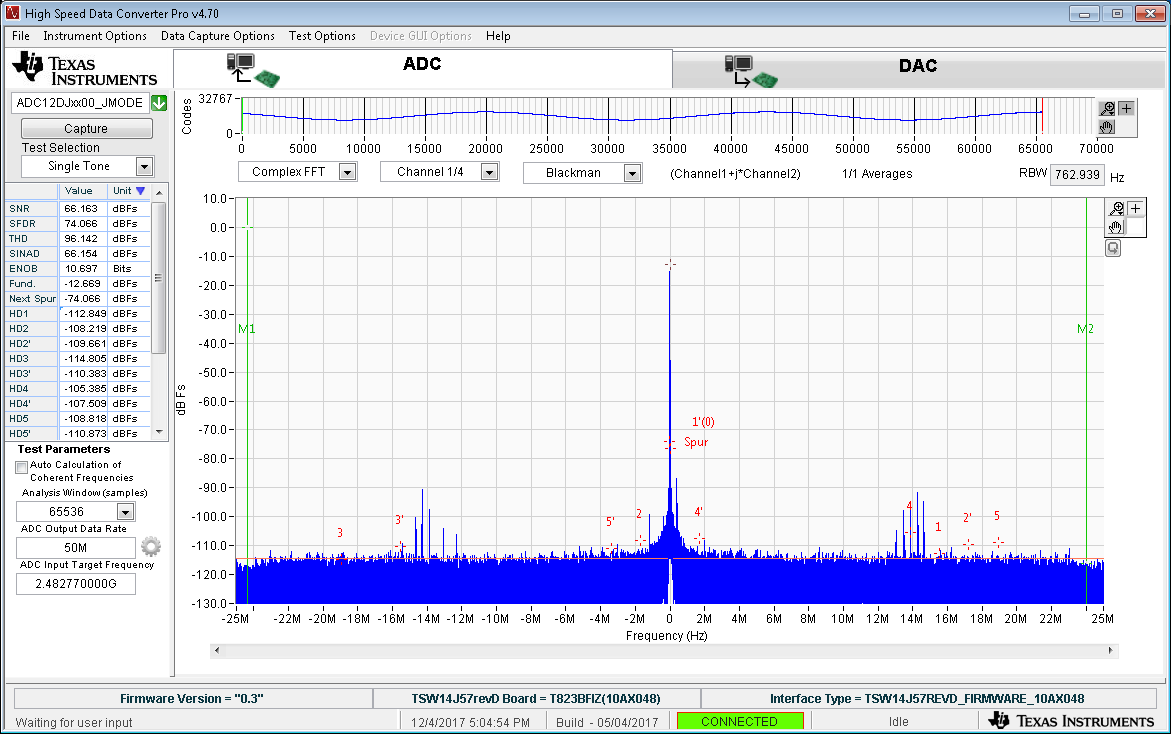

当我评估ADC12DJ3200 EVM时。 我配置了2700 MSPS,JMODE16 IT工作正常。 但是,当我使用JMODE 16配置为“800”MSP时,同样为JMODE0配置了MSP。 在这两种情况下都是抛出错误。 我已验证硬件D4 是否未闪烁且D3亮起。 我认为时钟不是从ADC板转到TSW FPGA 板。但根据数据表,它也应该支持800MSPS。我可以知道这一问题的原因是什么吗? 这是由于硬件限制还是缺少任何配置设置。