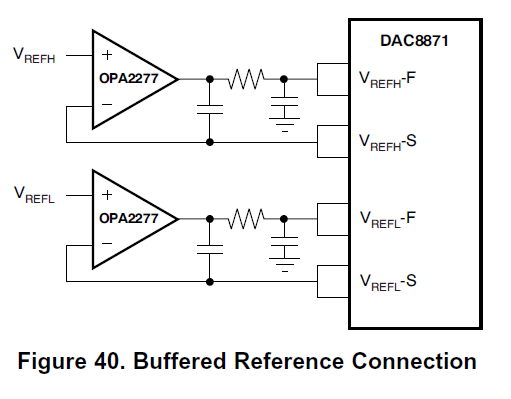

主题中讨论的其他部件: OPA4277, OPA2277

我正在目睹DAC8871输出上的一个有趣现象。 我知道主要的携带毛刺现象,但我所看到的远远超过数据表中的特征,并且表现似乎有所不同。 我绝不是在推动此设备的速度。 时钟频率为1.68 MHz。 VREFH=+10V。 VREFL=-10V。 参考随附的图像,有几个值得注意的项目:

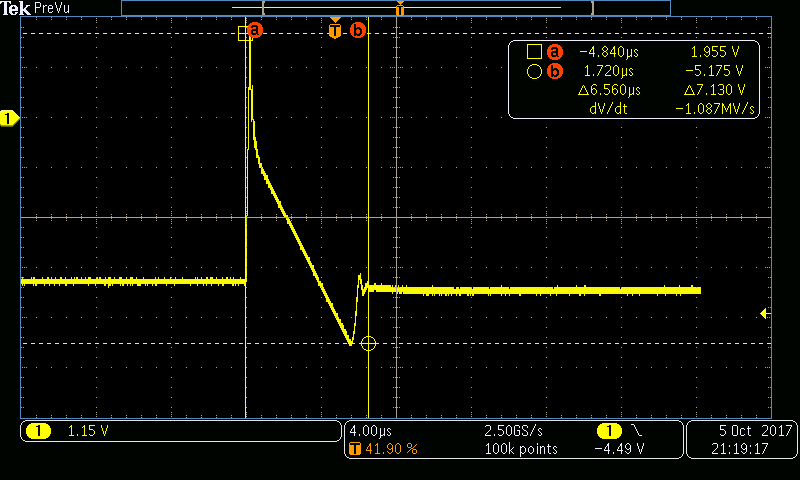

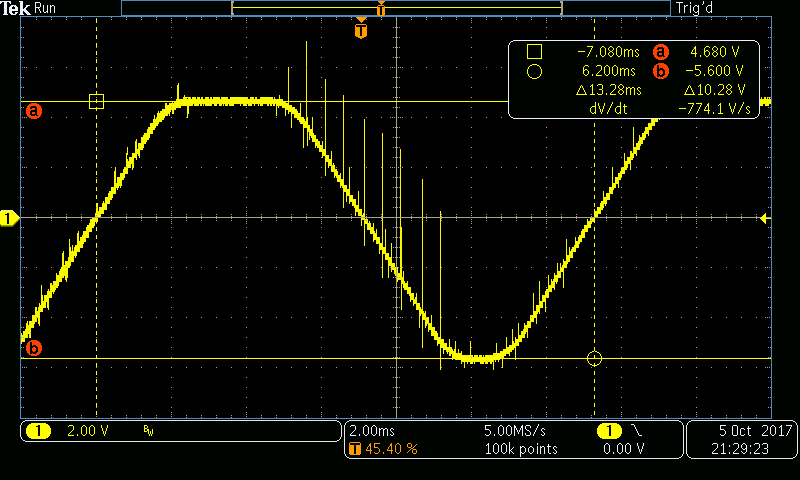

1. 在输出电压的适度0.156V步进(128 LSB)上,'毛刺'波动约为7V (+5.5V,-1.5V)。 参见image_01。

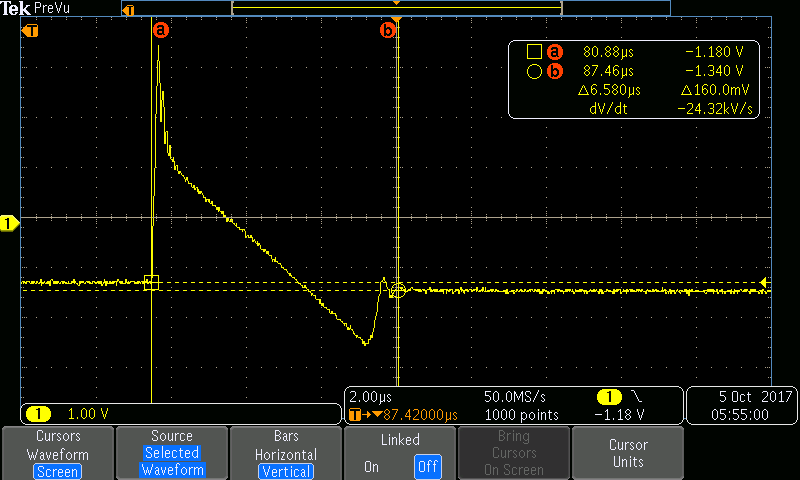

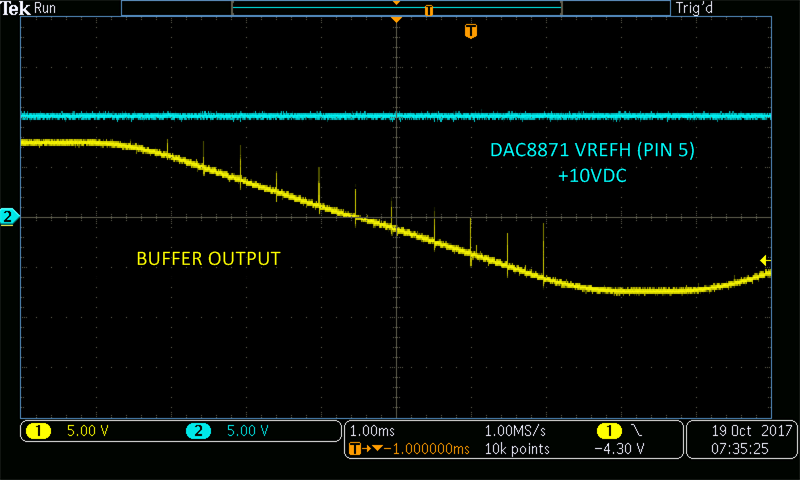

2. 与正常振铃甚至电容性电压摆动相比,"毛刺"在其大部分持续时间内似乎呈线性上升。 参见image_02。

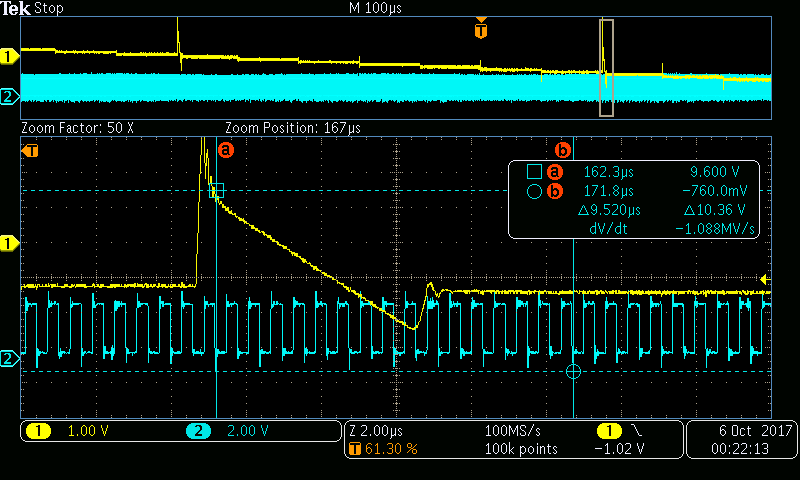

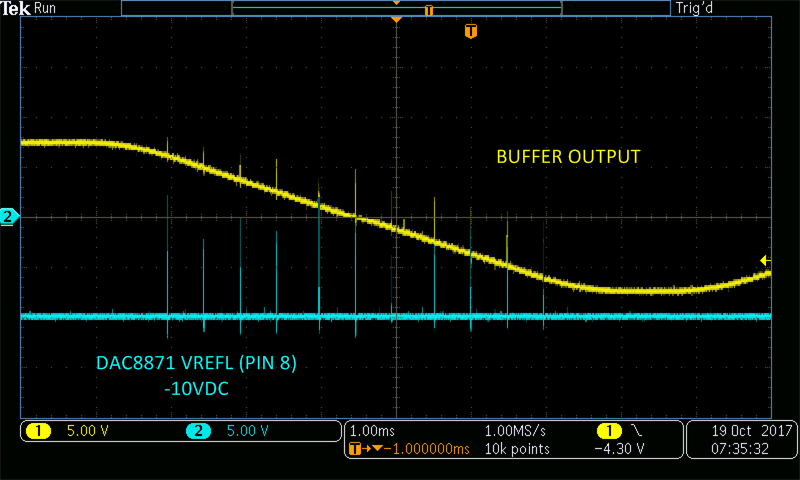

3. '毛刺'的持续时间持续11个时钟周期(~6.6 usec)。 参见image_03。

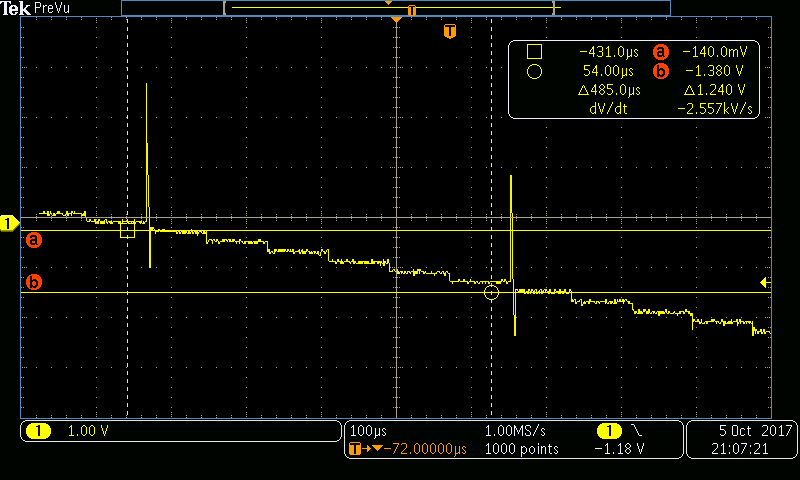

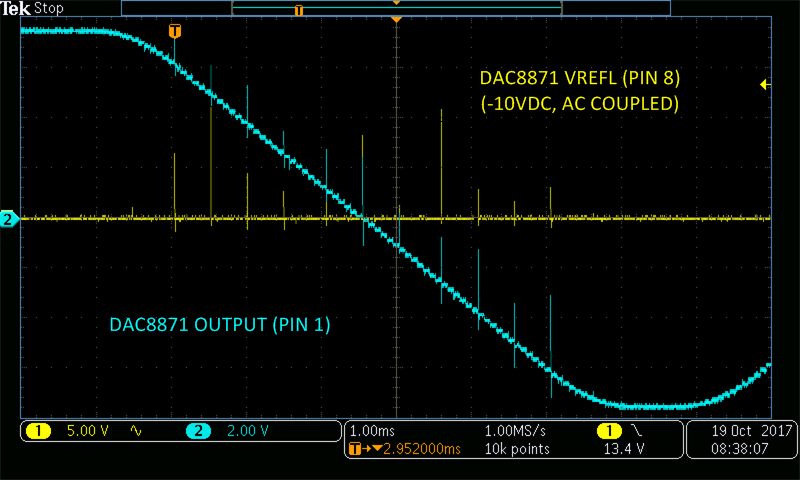

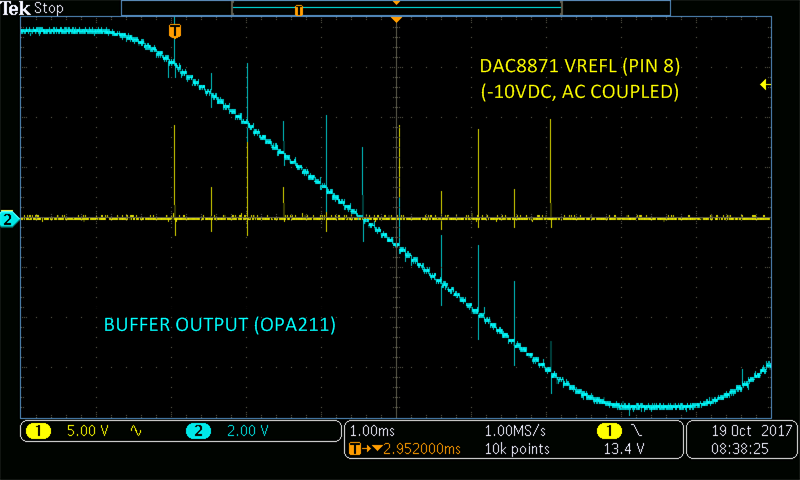

4. 在参考电压之间的斜坡序列上,'故障'会定期出现,对应于16 (4位)的代码变化。 参见image_04。

5. 最有趣的是,当代码渐减时,这些'小故障'的程度远比渐强。 参见image_05。

图片_ 01:

图像_02:

图片_ 03:

图片_04:

图片_05: