在“线程: ADS1274”中讨论的其他部件

您好,

我正在设计一种设备,它要求ADS1174 转换器采用菊花链式同步样片,通过使用电缆将它们连接到两个PCB上(每个PCB上一个ADC)。 您是否有关于类似用例的任何文档?

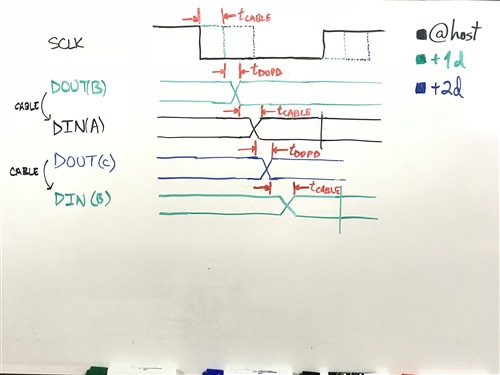

我想了解和评估这种设计的局限性,特别是在信号(时钟和数据)之间的时钟和可能延迟方面。

在数据表中,我找到了有关延迟以及数据如何从一台设备链接到下一台设备的信息。

"一个四通道ADS1174与另一个ADS1174的相位匹配可能不具有相同的采样匹配度(两个8通道ADS1178的情况相同)。 由于制造变化,内部CLK信号内部传播延迟的差异,加上到每个设备的外部CLK信号到达的差异,可能会导致更大的采样匹配错误。 长度相等的CLK跟踪或外部时钟分配设备可用于控制CLK信号的到达,以帮助减少采样匹配错误。"

这一问题来自第10页的"取样孔匹配"小节。 此处的"采样匹配错误"是指由于CLK信号延迟,一个ADC的输出采样与同一链中另一个ADC的输出采样不相位? 我没有找到量化此匹配错误的值。 它是否取决于CLK频率(如果CLK信号稍微不同步,降低频率会增加采样匹配度)?

"由于DOUT1和DIN都在SCLK的下降边缘偏移,DOUT1上的传播延迟会为DIN创建设置时间。 最小化SCLK中的歪斜,以避免超时。"

在这种情况下,传播延迟是从第一个ADS的DOUT1到第二个ADS的DIN的时间吗?

此外,我还了解到在帧同步串行模式下,“MSB数据在FSYNC进入高位之前在SCLK上升沿的DOUT上生效”。 这是否意味着MSB位仅在DOUT1上存在半个SCLK周期,因为后续位应在下一个下降边缘上移出?

您是否会有一个图表/时间图表来说明数据如何从一个ADC传播到下一个ADC?

非常感谢。

此致