主题中讨论的其他部件:ADC12D1620QML-SP,

您好,

我在接收器应用程序中使用ADC12D1600QML,其中:

采样率(FS)为1280 MHz;

输入音(Fin)为539.9 MHz (低于满刻度~3 dB)

使用多路复用器(2:1)模式;

使用非DES模式;

校准运行如数据表中所示

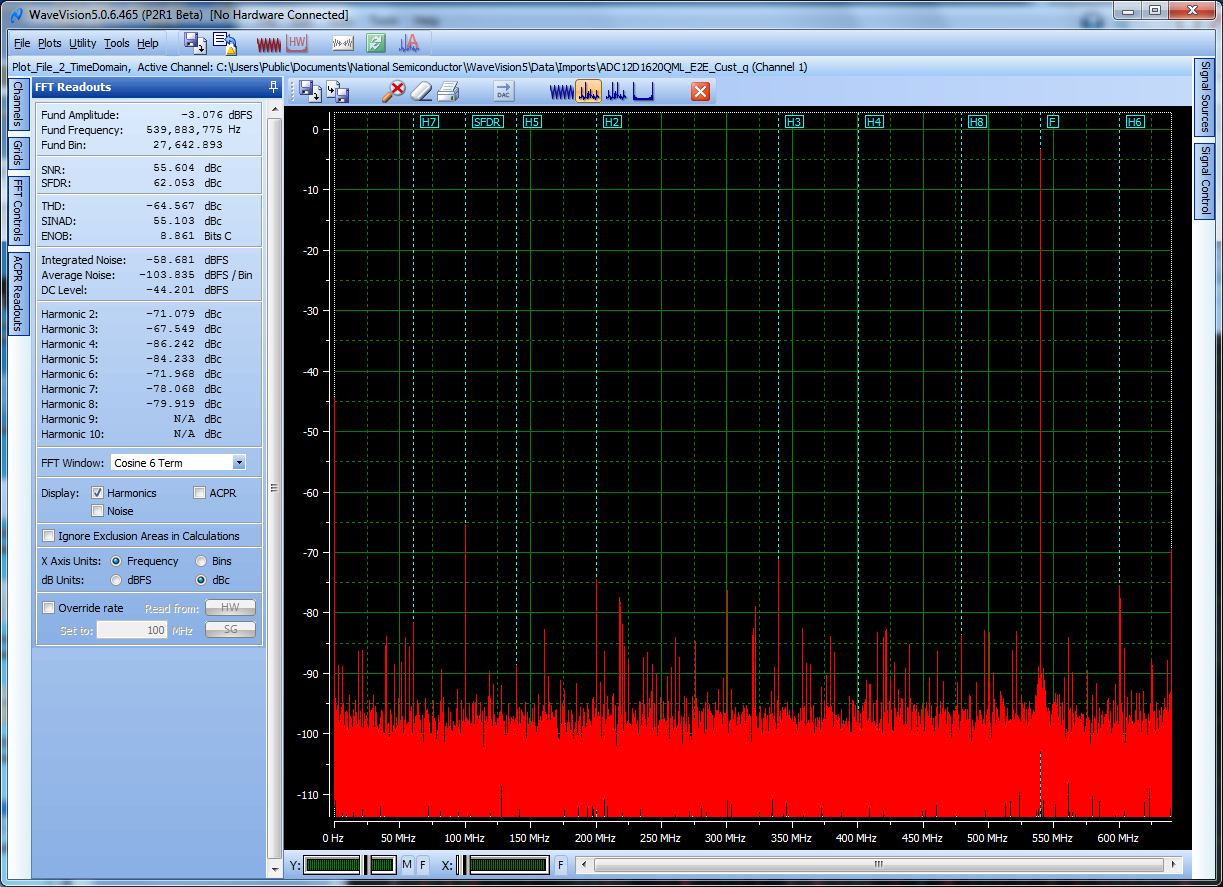

收集的数据显示由于DCLK耦合而预期的FS/4正频(320 MHz)。 不过,我们也在FS/4+Fin和FS/4-Fin. 这些spurs似乎与四子转换器操作(DES模式下的e.g.running)一致,但我不确定它们为什么出现在非DES配置中。 输入音经过过滤,使所有谐波/脉冲均为-75 dBc。 以下是来自I通道的原始FFT数据的"代表性"图解。

我们希望能就FS/4+Fin和FS/4-Fin为何采用非DES模式的问题提出任何想法。